#### REPUBLIQUE ALGERIENNE DEMOCRATIQUE ET POPULAIRE MINISTERE DE L'ENSEIGNEMENT SUPERIEUR ET DE LA RECHERCHE SCIENTIFIQUE

#### UNIVERSITE MOHAMED KHIDER DE BISKRA FACULTE DES SCIENCES ET DES SCIENCES DE L'INGENIEUR DEPARTEMENT D' ELECTRONIQUE

#### **MEMOIRE**

Présentée pour obtenir le diplôme de Magistère en Électronique

#### **Option**

Architecture des systèmes

# Conception d'amplificateurs opérationnels de transconductance Application à la réalisation de filtres Gm-C

#### PAR DHIABI FATHI

Le:

| <b>Président:</b>    | Pr. SENGOUGA Nour-Eddine   | Prof. | Univ. BISKRA |

|----------------------|----------------------------|-------|--------------|

| Rapporteur:          | Dr. MIMECHE Naamane        | MACC  | Univ. BISKRA |

| <b>Examinateurs:</b> | Pr. BOUGUECHAL Nour-Eddine | Prof. | Univ. BATNA  |

|                      | Dr. KHELIFA Ali            | MACC  | Univ. BISKRA |

|                      | Dr. BAARIR Zine-Eddine     | MACC  | Univ. BISKRA |

Année Scolaire 2004-2005

### Introduction

Les amplificateurs opérationnels de transconductance (OTA) appelés également cellule de transconductance Gm, sont des circuits relativement simples, qui permettent d'opérer à des fréquences élevées, tout en minimisant la puissance consommée. Ce sont des circuits vitaux dans les circuits électroniques, ceci est dû principalement à la commodité de réglage des paramètres des fonctions électroniques qu'ils réalisent par la transconductance. Le développement de l'architecture des OTAs et leurs applications dans les circuits intégrés a fait l'objet de nombreux travaux et n'a pas cessé de croître.

L'application des OTAs à la réalisation de filtres analogiques a acquis une grande popularité. Ils sont basés sur l'utilisation des intégrateurs Gm-C, d'où ils sont appelés les filtres Gm-C ou OTA-C.

L'intérêt des filtres Gm-C est qu'ils peuvent fonctionner dans une grande plage de fréquence allant de quelques Hz jusqu'à quelques GHz, en offrant la possibilité de contrôler leurs caractéristiques.

Sachant que la transconductance des OTAs peut être ajustée, il est possible de contrôler les paramètres (fréquence centrale, facteur de qualité et gain) de ces filtres.

L'objectif de ce mémoire est d'abord de concevoir des OTAs à simple sortie, à deux sorties, puis à quatre entrées et deux sorties, ayant de bonnes performances, ensuite, d'appliquer ces OTAs à la réalisation des filtres de type Gm-C.

La visibilité de ces circuits est montrée par simulation, en utilisant les paramètres des transistors MOS 0.8µm de AMS.

#### Chapitre 1

# Principales architectures de la cellule de transconductance CMOS

#### 1.1 INTRODUCTION

Les cellules de transconductance Gm sont des cellules qui effectuent une conversion de la tension d'entrée en un courant à la sortie. Elles peuvent être modélisées par une source de courant dépendant de la tension. Une cellule Gm idéale est une source de courant avec une impédance de sortie infinie. L'objectif de Gm est un paramètre important dans les applications nécessitant par exemple les filtres, qui est indépendante du process et de la variation de la température. Nous examinerons dans ce chapitre quelques architectures de la cellule de transconductance CMOS et les techniques associées pour améliorer la linéarité, basée sur les caractéristiques des transistors MOS.

#### 1.2 LE TRANSISTOR MOS

Plusieurs approches pour réaliser des transconductances linéaires en technologie CMOS ont été proposées. Quelques unes de ces approches emploient le transistor CMOS opérant dans la région de saturation, où l'expression du courant drain-source est donnée par la formule suivante:

$$I_{DS} = \beta (V_{GS} - V_T)^2$$

Pour  $V_{GS} > V_T$  et  $V_{DS} > V_{DS,sat}$  (1.1a)

Avec

$$\beta = \frac{Kp}{2} \left( \frac{W}{L} \right)$$

.

D'autres approches utilisent le transistor MOS opérant dans la région ohmique dont le courant drain-source est donné par l'équation suivante:

$$I_{DS} = 2 \beta \left( V_{GS} - V_T - \frac{V_{DS}}{2} \right) V_{DS}$$

Pour  $V_{GS} > V_T$  et  $V_{DS} < V_{DS,sat}$  (1.1b)

Dans ce cas la résistance du transistor MOS opérant dans la région ohmique est donnée par:

$$R = \frac{\partial V_{DS}}{\partial I_{DS}} = \frac{1}{2\beta (V_{GS} - V_{T})}$$

(1.1c)

#### 1.3 CELLULE DIFFERENTIELLE SIMPLE

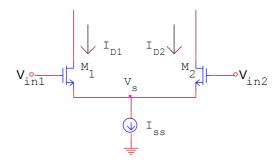

Figure 1.1 : Cellule différentielle à base du CMOS.

La première classe des cellules différentielles est réalisée par la paire des transistors MOS  $M_1$  et  $M_2$  du type N représentée par la figure 1.1 [1]. Cette paire de sources couplées est polarisée par une source de courant  $I_{SS}$ . Les deux tensions d'entrées  $Vin_1$  et  $Vin_2$  peuvent être appliquées sur les grilles de  $M_1$  et  $M_2$ , où les transistors  $M_1$  et  $M_2$  ont la même caractéristique. Le rôle de cette cellule est de convertir la tension d'entrée Vin en un courant  $I_{D1}$  et  $I_{D2}$  donné par les équations (1.2a) et (1.2b) dans la région de saturation des transistors de la figure 1.1.

$$I_{D1} = \beta \cdot (Vin_1 - V_S - V_T)^2$$

(1.2a)

$$I_{D2} = \beta \cdot (Vin_2 - V_S - V_T)^2$$

(1.2b)

En combinant (1.2a) et (1.2b), on trouve :

$$Vin_{1} - Vin_{2} = \sqrt{\frac{I_{D1}}{\beta}} - \sqrt{\frac{I_{D2}}{\beta}}$$

(1.3)

La somme des courants sur le nœud des sources des deux transistors est donnée par la formule suivante :

$$I_{D1} + I_{D2} = I_{SS} (1.4)$$

En combinant les équations (1.3) et (1.4), on obtient l'expression des courants drain des deux transistors, où  $\Delta V = Vin_1-Vin_2$ :

$$I_{D1} = \frac{I_{SS}}{2} + \beta \Delta V \sqrt{\frac{I_{SS}}{2\beta} - \left(\frac{\Delta V}{2}\right)^2}$$

(1.5a)

$$I_{D2} = \frac{I_{SS}}{2} - \beta \Delta V \sqrt{\frac{I_{SS}}{2\beta} - \left(\frac{\Delta V}{2}\right)^2}$$

(1.5b)

Les courants de sortie sont donnés pour  $|\Delta V| < \sqrt{\frac{I_{SS}}{\beta}}$ , c'est la région des saturations des transistors  $M_1$  et  $M_2$ . D'après les équations (1.5a) et (1.5b), on trouve les régions de saturations et de blocage de chaque transistor.

$$\begin{cases} Vin_1 > Vin_2 \\ \Delta V \ge \sqrt{\frac{I_{SS}}{\beta}} \end{cases} \Rightarrow \begin{cases} le \text{ transistor } M_1 \text{ est saturé, et le transistor } \\ M_2 \text{ est bloqué alors on a : } I_{D1} = I_{SS} \end{cases}$$

$$\begin{cases} Vin_2 > Vin_1 \\ \Delta V \le -\sqrt{\frac{I_{SS}}{\beta}} \end{cases} \Rightarrow \begin{cases} le \text{ transistor } M_2 \text{ est satur\'e, et le transistor } \\ M_1 \text{ est bloqu\'e alors on a : } I_{D2} = I_{SS} \end{cases}$$

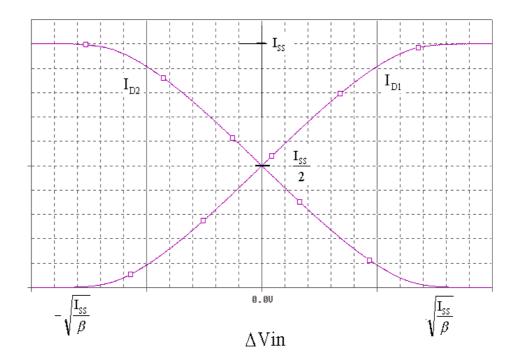

La figure 1.2 explique ces équations pour les courants de sortie en fonction de la tension d'entrée [2]. Ces courants de sortie sont limités par le courant de contrôle de la cellule différentielle I<sub>SS</sub>.

Figure 1.2 : Les courants drain de sortie de la paire de sources couplées en fonction de la tension d'entrée  $\Delta V$ .

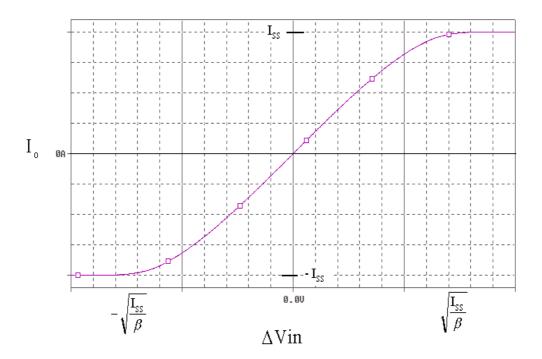

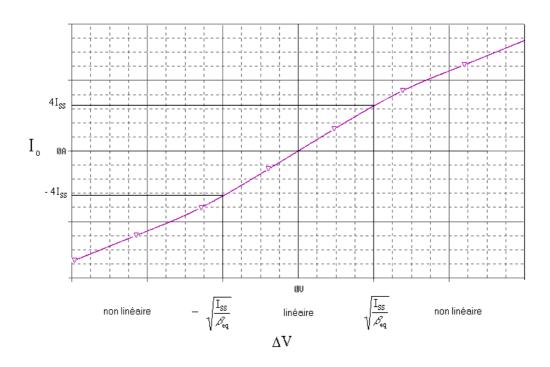

Le courant de sortie est donné par la différence des courants drain tel que:

$$I_{o} = I_{D1} - I_{D2} = \begin{cases} \Delta V \sqrt{2I_{SS}\beta} \sqrt{1 - \frac{\beta}{2I_{SS}}} \Delta V^{2} & \text{pour} \quad |\Delta V| \leq \sqrt{\frac{I_{SS}}{\beta}} \\ I_{SS} & \text{sign}(\Delta V) & \text{pour} \quad |\Delta V| > \sqrt{\frac{I_{SS}}{\beta}} \end{cases}$$

(1.6)

Cette équation est représentée par la figure (1.3) où la plage de tension d'entrée est limitée par  $\sqrt{\frac{I_{ss}}{\beta}}$  .

Figure 1.3 : La différence entre les courants de sortie de la paire de sources couplées en fonction de la variation de la tension d'entrée  $\Delta V$ .

#### 1.3.1 La transconductance en DC

La transconductance de la cellule différentielle simple est donnée par la dérivation de la différence des courants de sortie des drains des transistors  $M_1$  et  $M_2$  par rapport à la tension d'entrée, on obtient l'équation (1.7):

$$Gm_{DC} = \frac{\partial (I_{D1} - I_{D2})}{\partial \Delta V} = \frac{\sqrt{2I_{SS}\beta} \left[ 1 - \frac{\beta}{I_{SS}} \Delta V^2 \right]}{\sqrt{1 - \frac{\beta}{2I_{SS}}} \Delta V^2}$$

(1.7)

#### 1.3.2 La transconductance en AC

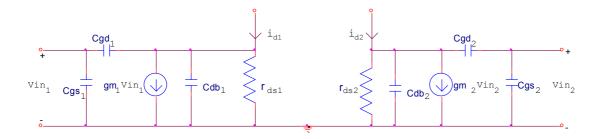

Figure 1.4 : Le modèle petit signal équivalent d'une cellule différentielle simple.

Pour avoir une comparaison entre la transconductance en mode DC avec la transconductance en mode AC [3], on remplace les transistors MOS  $M_1$  et  $M_2$  de la figure 1.1 par leur modèle équivalent en petit signal comme donné sur la figure 1.4. Pour une entrée en mode différentiel  $V_{in1}$  =- $V_{in2}$  = $\frac{\Delta V}{2}$  [3,4], on obtient les transconductances pour chaque transistor MOS :

$$gm_{1} = \frac{\partial I_{D1}}{\partial V_{GS1}} = 2\frac{\partial I_{D1}}{\partial \Delta V} = \frac{\sqrt{2I_{SS}\beta} \left[1 - \frac{\beta}{I_{SS}}\Delta V^{2}\right]}{\sqrt{1 - \frac{\beta}{2I_{SS}}\Delta V^{2}}}$$

(1.8a)

$$gm_{2} = \frac{\partial I_{D2}}{\partial V_{GS2}} = -2\frac{\partial I_{D2}}{\partial \Delta V} = \frac{\sqrt{2I_{SS}\beta} \left[1 - \frac{\beta}{I_{SS}} \Delta V^{2}\right]}{\sqrt{1 - \frac{\beta}{2I_{SS}} \Delta V^{2}}}$$

(1.8b)

On a une même valeur de transconductance  $(gm_1=gm_2)$  qui est la transconductance en mode DC, soit dans la demi-cellule de la figure 1.4 on trouve :

$$i_{d1} = \frac{gm_1 \left(1 - \frac{C_{GD1}}{gm_1} s\right)}{1 + r_{ds1} C_{DS1} s} v_{in1}$$

(1.8c)

Pour la résistance drain-source dans la paire de sources couplées et infinie, on trouve la relation entre la différence des courants de sortie des drains et la tension d'entrée :

$$i_0(s) = i_{d1}(s) - i_{d2}(s) = gm_1 V_{in1}(s) - gm_2 V_{in2}(s)$$

(1.9)

à partir de l'équation (1.8) et (1.9) on trouve:

$$i_{o}(s) = Gm_{DC} \Delta V(s)$$

(1.10)

On remarque que la transconductance en AC c'est la même en DC, lorsque en élimine l'effet interne (la résistance drain-source et les capacités des transistors MOS).

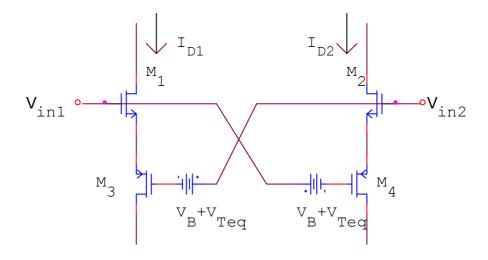

#### 1.4 LA LINEARITE DE LA DOUBLE PAIRE DIFFERENTIELLE CROISÉE

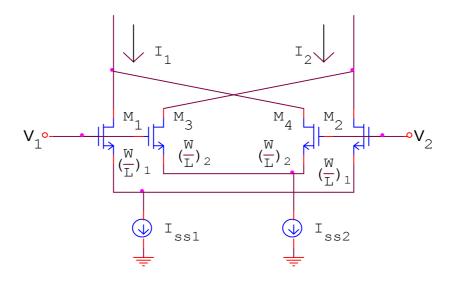

Une augmentation substantielle dans la linéarité peut être obtenue en croisant deux paires différentielles selon la figure 1.5 [1]. Les dimensions des transistors MOS  $M_{1,2}$  et  $M_{3,4}$  sont respectivement  $(W/L)_1$  et  $(W/L)_2$ . Le but de cette configuration est de faire varier le courant du drain de chaque branche de  $M_1$  et  $M_2$  de la cellule simple par l'utilisation d'une deuxième cellule  $M_3$  et  $M_4$  avec un courant de polarisation  $I_{SS2}$  (figure1.5). Cette configuration exige des conditions sur les dimensions des transistors MOS, et sur les valeurs des courants de polarisation, pour l'annulation approximative des non linéarités.

Figure 1.5: Double paire Différentielle croisée.

A partir de l'équation (1.6) en qualifiant cette architecture pour  $I_{SS1} > I_{SS2}$ , alors on trouve la relation (1.11b) de la différence entre les courants  $I_1$  et  $I_2$  de sortie de chaque branche du circuit comme montré sur la figure 1.5.

$$I_{O} = I_{1} - I_{2} = (I_{D1} - I_{D2}) - (I_{D3} - I_{D4})$$

(1.11a)

$$I_{O} = \begin{cases} \left(\sqrt{2I_{SS1}\beta_{1}}\sqrt{1 - \frac{\beta_{1}}{2I_{SS_{1}}}}(\Delta V)^{2} - \sqrt{2I_{SS2}\beta_{2}}\sqrt{1 - \frac{\beta_{2}}{2I_{SS_{2}}}}(\Delta V)^{2}\right)\Delta V & \text{pour } |\Delta V| \leq \sqrt{\frac{I_{SS2}}{\beta_{2}}} \\ \sqrt{2I_{SS1}\beta_{1}}\sqrt{1 - \frac{\beta_{1}}{2I_{SS_{1}}}}(\Delta V)^{2} - I_{SS2}\text{sign}(\Delta V) & \text{pour } \sqrt{\frac{I_{SS2}}{\beta_{2}}} \leq |\Delta V| \leq \sqrt{\frac{I_{SS1}}{\beta_{1}}} \\ \left(I_{SS1} - I_{SS2}\right) \text{sign}(\Delta V) & \text{pour } |\Delta V| \geq \sqrt{\frac{I_{SS1}}{\beta_{1}}} \end{cases}$$

$$. \tag{1.11b}$$

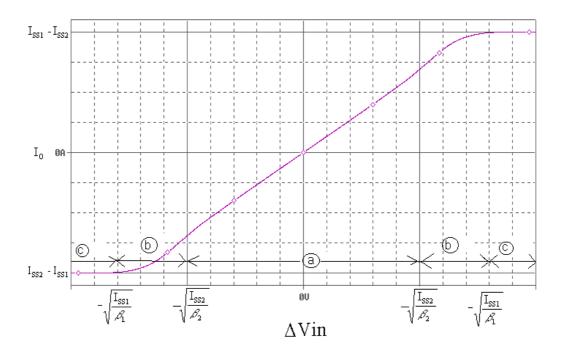

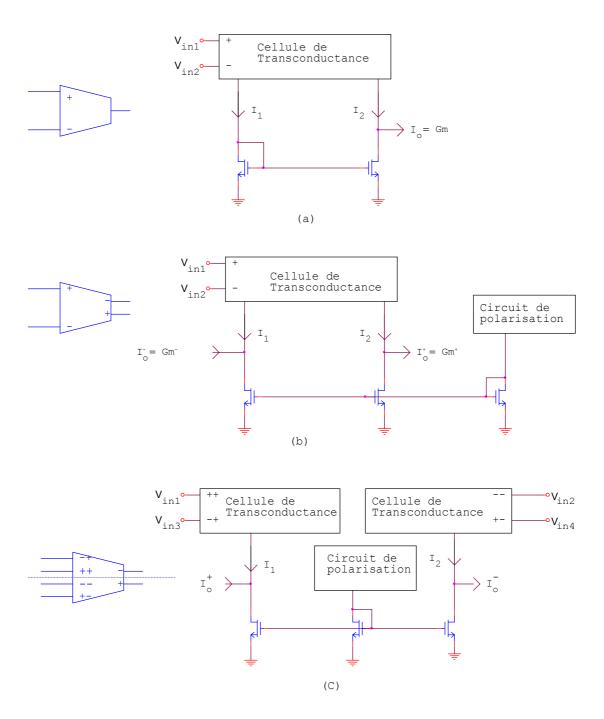

Sur le graphe de la figure 1.6 sont montrées les trois régions qui représentent les trois formules (1.11b) sur l'intervalle de saturation et le blocage des transistors. La région (a) c'est la région de saturation de tous les transistors, la région (b) c'est la région de saturation de  $M_1$  et  $M_2$ . Dans cette région, la deuxième cellule est donnée seulement le courant de polarisation  $I_{SS2}$  à partir du fonctionnement de l'un des deux transistors de la paire correspondante, et la région (c) c'est la région du fonctionnement de l'un des deux transistors sur chaque cellule qui donne une différence entre les courants de polarisation  $I_{SS1}$ - $I_{SS2}$ :

Figure 1.6 : Le courant de sortie en fonction de la tension d'entrée de la double paire différentielle croisée.

Donc l'étude de la linéarité donnée dans la région de saturation de tous les transistors exige une condition sur leur dimension. L'augmentation de la linéarité est donnée à partir du premier harmonique  $a_1$  du développement en série, du courant de sortie  $I_{O}$ , selon l'équation suivante :

$$I_0 = a_1 \times \Delta V + a_2 \times \Delta V^2 + a_3 \times \Delta V^3 + \dots$$

(1.12a)

$$\begin{cases}

a_1 = \sqrt{2I_{SS1}\beta_1} - \sqrt{2I_{SS2}\beta_2} \\

a_2 = 0 \\

a_3 = \frac{1}{2\sqrt{2}} \times \left(\frac{\beta_1^{\frac{3}{2}}}{\sqrt{I_{SS1}}} - -\frac{\beta_2^{\frac{3}{2}}}{\sqrt{I_{SS2}}}\right)

\end{cases} (1.12b)$$

Pour avoir une bonne linéarité, on néglige la troisième harmonique  $a_3$ , on obtient une nouvelle condition pour une faible tension d'entrée, sur les dimensions des transistors MOS et les courants de polarisation selon l'équation (1.13).

$$\left[\frac{\left(\frac{W}{L}\right)_{1}}{\left(\frac{W}{L}\right)_{2}}\right]^{3/2} = \left[\frac{Iss_{1}}{Iss_{2}}\right]^{1/2}$$

(1.13)

Pour  $(W/L)_1 \neq (W/L)_2$  et  $I_{SS1} \neq I_{SS2}$  cela rend le coefficient du terme linéaire  $a_1$  différent de zéro, en appliquant l'équation (1.13) dans (1.12) on obtient :

$$I_{O} = \left(\sqrt{2I_{SS1} \beta_{1,2}} - \sqrt{2I_{SS2} \beta_{3,4}}\right) \Delta V$$

(1.14)

Les termes non linéaires s'annulent, de cela on déduit la transconductance générale qui est la différence des transconductances de chaque cellule, qui est donnée par la relation suivante :

$$Gm = Gm_1 - Gm_2 = \sqrt{2I_{SS1} \beta_{1,2}} - \sqrt{2I_{SS2} \beta_{3,4}}$$

(1.15)

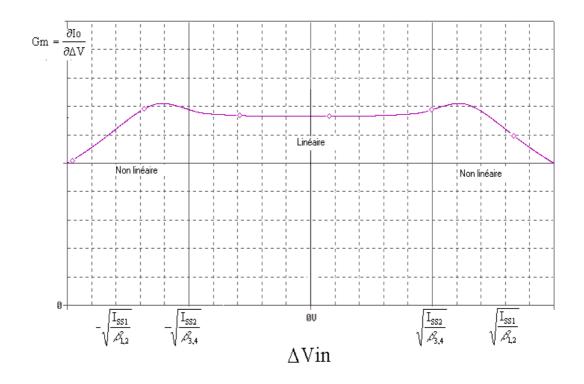

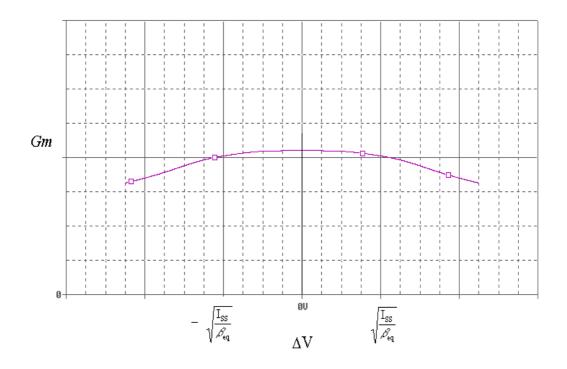

La transconductance en fonction de la tension d'entrée est représentée par la figure 1.7.

Figure 1.7 : Intervalle de linéarité de la transconductance.

La transconductance en AC est la même qu'en DC pour chaque cellule  $(M_1,M_2)$  et  $(M_3,M_4)$  sur la figure 1.5 déjà étudiée dans la section 1.3.2, donc par leur croisement on trouve la transconductance générale qui est la différence de transconductance de chaque cellule [4].

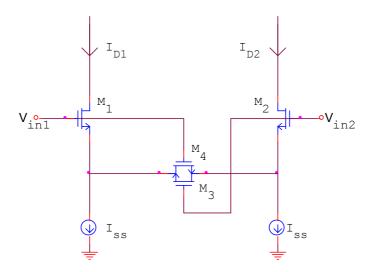

# 1.5 CELLULE DE TRANSCONDUCTANCE OPERANT DANS LA REGION OHMIQUE

Il existe plusieurs types de cellules de transconductance opérant dans la région ohmique, le circuit montré à la figure 1.8, représente une architecture typique à cette catégorie [4]. Bien qu'ayant le nom d'une cellule opérant dans la région ohmique,ou seuls les transistors  $M_3$  et  $M_4$  se trouvent dans ce mode, les autres transistors étant en saturation. La transconductance de ce circuit, peut être modifiée par la résistance R du transistor  $M_3$  et  $M_4$  équation (1.16).

Figure 1.8: Cellule opérant dans la région ohmique.

$$R = \frac{1}{2\beta (V_{GS3,4} - V_T)}$$

(1.16)

#### 1.6 TECHNIQUES DE LINEARISATION

Plusieurs techniques pour améliorer la linéarité de la cellule de transconductance CMOS ont été proposées. La plupart de ces techniques peuvent être classées en deux catégories [1], la classe AB, et la paire couplée à polarisation contrôlée. Quelques transconductances utilisent une ou plusieurs de ces techniques pour obtenir une bonne linéarité.

#### 1.6.1 Cellule de transconductance en Classe AB

#### 1.6.1.1 Principe de base de la cellule

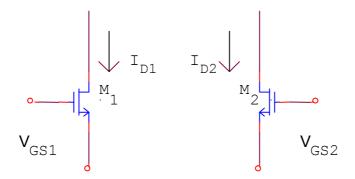

Figure 1.9 : Le circuit de deux transistors démontrant le principe de classe AB.

La transconductance en classe AB est basée sur les caractéristiques des transistors MOS dans la région de saturation, qui comprend deux transistors comme représenté sur la figure 1.9[1], les courants de sortie de cette cellule sont donnés par :

$$I_{D1} = \beta (V_{GS1} - V_T)^2$$

pour  $V_{GS1} > V_T$  (1.17a)

$$I_{D2} = \beta (V_{GS2} - V_T)^2$$

pour  $V_{GS2} > V_T$  (1.17b)

En écrivant  $V_{CM} = \frac{(V_{GS1} + V_{GS2})}{2}$ , la tension en mode commun, et  $\Delta V = V_{GS1} - V_{GS2}$ , la tension en mode différentiel, on trouve les courants de chaque drain des transistors  $M_1$  et  $M_2$  à partir de la formule (1.17):

$$I_{D1} = \beta \left( \frac{\Delta V}{2} + V_{CM} - V_{T} \right)^{2}$$

pour  $\Delta V > -2 (V_{CM} - V_{T})$  (1.18a)

$$I_{D2} = \beta \left( -\frac{\Delta V}{2} + V_{CM} - V_{T} \right)^{2}$$

pour  $\Delta V < 2 (V_{CM} - V_{T})$  (1.18b)

La différence entre ces deux courants, donne le courant suivant:

$$I_{\text{diff}} = I_{D1} - I_{D2} = 2\beta(V_{CM} - V_T) \Delta V$$

Pour  $|\Delta V| < 2(V_{CM} - V_T)$  (1.19)

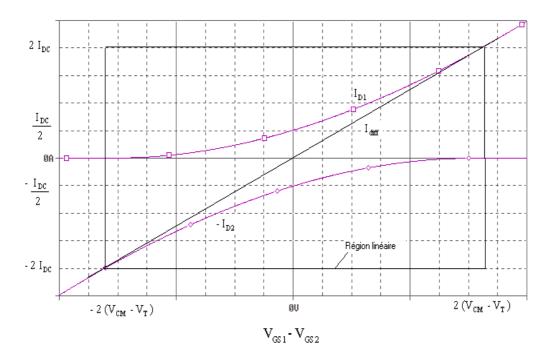

L'équation 1.19 indique qu'une transconductance linéaire peut être obtenue en s'assurant que la somme des tensions grille-source est constante [1].

La transconductance est donnée par  $Gm = 2\beta (V_{CM} - V_T)$ , elle est parfaitement linéaire et peut être ajustée en fonction de la tension d'entrée en mode commun. L'intervalle de linéarité est donné pour la région de saturation des transistors  $|\Delta V| < 2(V_{CM} - V_T)$ . Sur la figure 1.10 est représentée les formules (1.18a), (1.18b) et (1.19). Le courant de sortie linéaire maximum est donné dans la région de tension d'entrée différentielle  $|\Delta V| = 2(V_{CM} - V_T)$ , où le courant de sortie est donné par :

$$I_{D1,2} = 2 I_{DC} = 4 \beta (V_{CM} - V_{T})^{2}$$

(1.20)

Figure 1.10 : Les courants de sortie  $I_{D1}$  ,  $I_{D2}$  , et  $I_{dif}$  en fonction de la tension d'entrée différentielle.

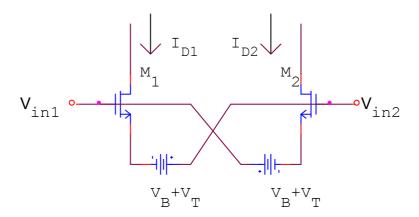

#### 1.6.1.2 La double paire couplée par croisement

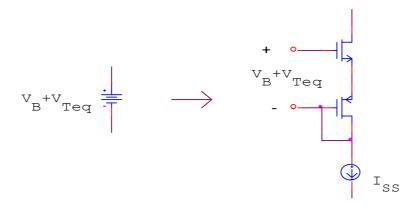

Figure 1.11: Le principe de linéarité de la transconductance en classe AB basé sur le circuit de la figure 1.9.

Une autre alternative du principe du circuit de transconductance en classe AB de la figure 1.9 est d'ajouter à ce circuit deux source de tension entre la grille de  $M_1$  et la source de  $M_2$  et entre la grille de  $M_2$  et la source de  $M_1$  comme montrée sur

la figure 1.11. Dans ce circuit la somme des tensions grille-Source de  $M_1$  et  $M_2$  doit être constante afin d'annuler les non linéarités. La tension en mode commun est donnée par:

$$V_{GS1} + V_{GS2} = 2(V_B + V_T)$$

(1.21a)

et la tension en mode différentiel est donnée par:

$$V_{GS1}-V_{GS2} = V_{in1}-V_{in2} = \Delta V$$

(1.21b)

la substitution de (1.21a,b) dans (1.18) permet d'obtenir:

$$I_0 = I_{D1} - I_{D2} = 4 \beta V_B \Delta V$$

(1.22)

La transconductance  $Gm=4\beta V_B$  est parfaitement linéaire et peut être ajustée en changeant la tension de polarisation  $V_B$ .

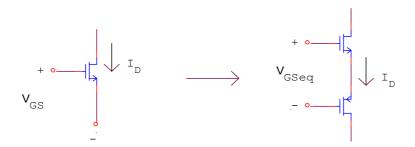

Les sources de tension de la figure 1.11 doivent rester constantes indépendamment du courant le traversant. En outre, les sources de tension ne doivent pas diriger le courant des bornes d'entrée afin de maintenir la résistance de l'entrée élevée. Une autre solution est donnée par les transistors MOS double qui agit comme un seul transistor figure 1.12 avec  $V_T$  est remplacé par  $V_{Teq}$  (équation 1.24a),et  $\beta$  remplacé par  $\beta$  (équation 1.24b).

Figure 1.12: Remplacement du transistor simple par la double paire CMOS.

$$V_{GSeq} = V_{GSn} + V_{GSp} \tag{1.23a}$$

$$V_{GSeq} = \left(\frac{1}{\sqrt{\beta_n}} + \frac{1}{\sqrt{\beta_p}}\right)\sqrt{I_D} + V_{Tn} + \left|V_{Tp}\right|$$

(1.23b)

En remplaçant les  $V_{Teq}$  et  $\beta_{eq}$  par leur équivalent :

$$V_{\text{Teq}} = V_{\text{Tn}} + \left| V_{\text{Tp}} \right| \tag{1.24a}$$

$$\beta_{\text{eq}} = \frac{\beta_{\text{n}} \beta_{\text{p}}}{(\sqrt{\beta_{\text{n}}} + \sqrt{\beta_{\text{p}}})^2}$$

(1.24b)

On obtient le résultat du courant drain de la double paire CMOS équivalant :

$$I_{D} = \beta_{eq} (V_{GSeq} - V_{Teq})^{2}$$

$$(1.25)$$

Une solution bien meilleure peut être réalisée en remplaçant les transistors  $M_1$  et  $M_2$  sur la figure 1.11 par des paires de transistors MOS double, comme présentée sur la figure 1.13, Il faut noter cependant que les courants drain en  $M_1$  et  $M_2$  ne traversent plus les sources de tension flottantes et que les courants dans  $M_3$  et  $M_4$  sont en fonction de la tension d'entrée.

Figure 1.13 : Remplacement des transistors d'entrée par la doubles paires CMOS pour la figure 1.11.

Les sources de tension flottantes peuvent être réalisées par une paire de transistor MOS double dont l'un est reliée comme une diode, polarisé par un courant  $I_{SS}$  comme représenté sur la figure 1.14, la tension de polarisation  $V_B$  est donnée par:

$$V_{\rm B} = \sqrt{\frac{I_{\rm SS}}{\beta_{\rm eq}}} \tag{1.26}$$

Figure 1.14 : L'équivalent de la source de tension flottante par une paire de transistor MOS double.

Figure 1.15 : La paire double couplée par croisement en Classe AB.

En introduisant le circuit de polarisation de la figure 1.14 dans le circuit de la figure 1.13 on obtient le circuit comme représenté dans la figure 1.15. En combinant, l'équation (1.22) et l'équation (1.26) on trouve:

$$I_{O} = I_{1} - I_{2} = 4\sqrt{I_{SS}\beta_{eq}} \quad \Delta V \quad \text{pour} \quad \Delta V \le \sqrt{\frac{I_{SS}}{\beta_{eq}}}$$

(1.27)

La transconductance est parfaitement linéaire figure 1.16 et peut être ajustée par la variation du courant de polarisation  $I_{SS}$ . La gamme linéaire est considérablement meilleure par l'utilisation de la paire de transistor CMOS ( $\beta_{eq} < \beta_n.\beta_p$ ). Cependant le courant de sortie est linéaire jusqu'a  $4I_{SS}$  comme montrée dans la figure 1.17.

Figure 1.16 : Intervalle de la linéarité de la cellule de transconductance.

Figure 1.17 : Le courant de sortie  $I_{\rm O}$ , en fonction de la variation de tension d'entrée  $\Delta V$ .

#### 1.6.2 La paire couplée de transconductance à polarisation contrôlée

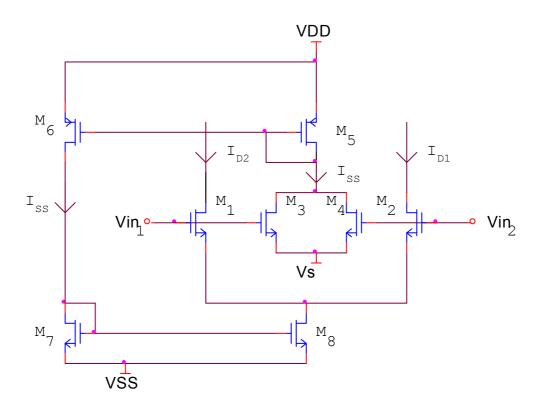

Figure 1.18: Cellule différentielle de transconductance avec un nouveau circuit de polarisation.

En remplacant la source de courant sur la cellule différentielle simple de la figure 1.1 par un circuit qui génère un courant de polarisation dépendant de la tension d'entrée  $\Delta V$ , présenté sur la figure 1.18 [1,5].On a la somme des courants drain des transistors de  $M_3$  et  $M_4$  qui donne le courant de polarisation  $I_{SS}$  présenté par l'équation (1.29), le rôle des transistors  $M_5$ ,  $M_6$ ,  $M_7$  et  $M_8$  c'est de transmettre le courant de polarisation vers la paire de transistors  $M_1$  et  $M_2$  couplée.

$$I_{D3} = \beta_{3,4} \cdot (Vin_1 - V_S - V_T)^2$$

(1.28a)

$$I_{D4} = \beta_{34} \cdot (Vin_2 - V_S - V_T)^2$$

(1.28b)

La somme entre ces courants :

$$I_{SS} = I_{D3} + I_{D4} = 2\beta_{3,4} (V_{CM} - V_{T})^{2} + \frac{\beta_{3,4}}{2} \Delta V^{2}$$

(1.29)

Où  $V_{\text{CM}}$  c'est la tension d'entrée en mode commun qui est égale à :

$$V_{CM} = \frac{V_{in1} + V_{in2}}{2} - V_{S}$$

(1.30)

Par remplacement de l'équation 1.29 dans l'équation (1.6) on obtient le résultat suivant:

$$I_{o} = \begin{cases} \Delta V \sqrt{2I_{DC}\beta} \sqrt{1 - \frac{\beta - \beta_{3,4}}{2I_{DC}}} \Delta V^{2} & \text{pour} \quad |\Delta V| \leq \sqrt{\frac{2I_{DC}}{\beta}} \\ I_{DC} + \beta_{3,4} \Delta V^{2} & \text{pour} \quad |\Delta V| > \sqrt{\frac{2I_{DC}}{\beta}} \end{cases}$$

(1.31)

Où I<sub>DC</sub> est un courant déterminé par l'équation suivante:

$$I_{DC} = 2\beta_{3,4} (V_{CM} - V_{T})^{2}$$

(1.32)

On obtient une transconductance linéaire Gm =  $\sqrt{2I_{DC}\,\beta}$  pour  $\beta_{3,4}$ = $\beta$ , qui est non limitée par  $I_{SS}$ .

Figure 1.19: Les caractéristiques du courant de sortie de la paire différentielle simple avec la polarisation simple et la polarisation contrôlée.

La figure 1.19 représente le courant de sortie en fonction de la tension d'entrée de la formule 1.28 du circuit avec la polarisation contrôlée, qui donne une augmentation sur l'intervalle de linéarité d'un facteur de  $\sqrt{2}$  par rapport au circuit avec polarisation simple. La transconductance en AC et DC est la même, ceci est du que la cellule différentielle est la même seulement ce qui change c'est la polarisation.

#### 1.7 **CONCLUSION:**

Au cours du présent chapitre, on a présenté une revue de principales architectures de cellules de transconductances CMOS. L'accent a été mis sur la détermination de la transconductance et les techniques associées pour améliorer la linéarité.

### Chapitre 2

# Conception d'amplificateurs opérationnels de transconductance

#### 2.1 INTRODUCTION

L'amplificateur Opérationnel de Transconductance, appelé OTA ou cellule de transconductance Gm, avec comme entrée la tension et comme sortie le courant, réalise un processus de conversion tension courant qui permet d'obtenir une transconductance. Ainsi, plusieurs architectures d'OTA ont été proposées afin de répondre aux exigences de diverses applications. On distingue plusieurs grandes classes d'architecture d'OTA: OTA avec sortie simple et OTA avec multiple sorties, ainsi que des OTAs avec plusieurs entrées et plusieurs sorties. Ces différentes classes sont obtenues en ajoutant quelques améliorations sur les OTAs à sortie simple.

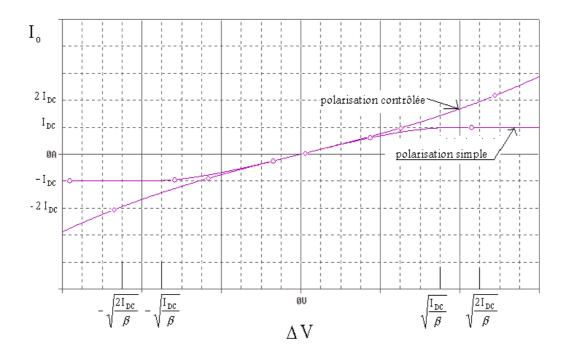

# 2.2 REALISATION STRUCTURELLE D'AMPLIFICATEUR OPERATIONNEL DE TRANSCONDUCTANCE

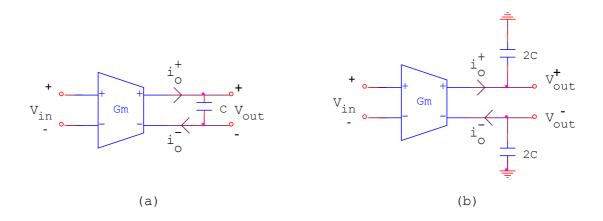

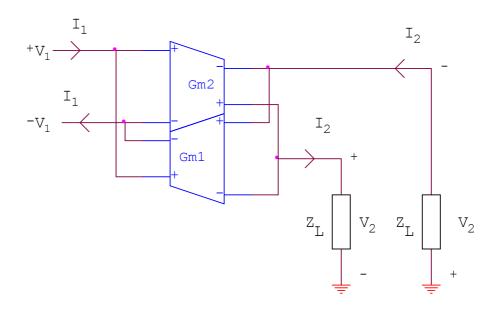

La plupart des amplificateurs opérationnels de transconductance ont la même structure de base "sortie unique", on peut ajouter sur cette structure de base des circuits qui permettent d'avoir plusieurs entrée en tension et plusieurs sorties de courant. La structure de base est donnée pour une sortie unique est représentée sur la figure 2.1, cette structure permet d'avoir une transconductance Gm à partir de la différence entre les courants  $I_1$  et  $I_2$ , obtenue à partir de la conversion de tension entrée  $\Delta V = V_{in1} - V_{in2}$ , par la cellule de transconductance comme montré sur la figure 2.1a, et on ajoute un circuit de polarisation (figure 2.1b) qui permet d'éliminer les non linéarités sur chaque branche. Cette structure générale permet d'avoir une double sortie en courant avec des transconductances de même valeur absolue mais de signe contraire comme est montré sur la figure 2.1b, ou  $Gm^+=|Gm^-|$ .

Cet amplificateur de transconductance différentielle permette de réaliser plus de fonction que le circuit OTA à sortie unique. Pour avoir plus d'entrée en tension et sortie en courant on ajoute deux ou plusieurs structures simples qui permettent la conversion tension-courant comme est montré dans la figure 2.1c, et en utilisant le même circuit de polarisation qui élimine les non linéarités.

Figure 2.1: (a) Structure d'un OTA sortie unique.

- (b) Structure d'un OTA différentielle.

- (c) Structure d'un OTA différentielle avec quatre entrées.

## 2.3 AMPLIFICATEUR OPERATIONNEL DE TRANSCONDUCTANCE SIMPLE

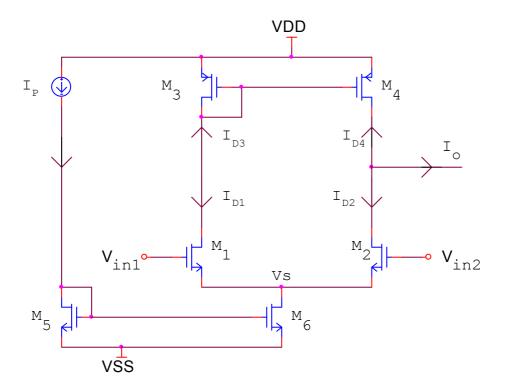

L'architecture de base pour réaliser l'amplificateur opérationnel de transconductance à sortie unique est représentée sur la figure 2.2 [2]. Cette structure a été utilisée comme étage d'entrée dans la plupart des amplificateurs opérationnels.

Figure 2.2 : Amplificateur opérationnel de transconductance simple.

Ce circuit représenté sur la figure 2.2 est composé de trois éléments :-

a- La cellule différentielle réalisée par une paire de source couplée de type N ( $M_1$  et  $M_2$ ), est une cellule de différentielle simple qui permet de convertir les tensions d'entrée  $V_{in1}$  et  $V_{in2}$  en un courant à la sortie de leur drain qui sont donnés à partir des relations suivante concernant les transistors MOS dans la région de saturation :

$$I_{D1} = \frac{I_{P}}{2} + \beta \Delta V \sqrt{\frac{I_{P}}{2\beta} - \left(\frac{\Delta V}{2}\right)^{2}}$$

(2.1a)

$$I_{D2} = \frac{I_{P}}{2} + \beta \Delta V \sqrt{\frac{I_{P}}{2\beta} - \left(\frac{\Delta V}{2}\right)^{2}}$$

(2.1b)

- b- Un circuit de polarisation qui permet de faire varier la transconductance Gm= f(I<sub>P</sub>) en fonction d'une source de courant variable I<sub>P</sub>. Pour ne pas affecter la tension de grille-source V<sub>GS1</sub> et V<sub>GS2</sub> par la tension de polarisation, on ajoute un miroir de courant composé par les transistors M<sub>5</sub> et M<sub>6</sub>.

- c- Un circuit miroir de courant composé par les transistors MOS de type P (M<sub>3</sub> et M<sub>4</sub>) qui permet de copier le courant I<sub>D3</sub>=-I<sub>D1</sub> en un courant I<sub>D4</sub>=I<sub>D3</sub>, ce qui donne le courant de sortie, qui est la différence entre les courants I<sub>D4</sub> et I<sub>D2</sub>, comme suit:

$$I_0 = I_{D4} - I_{D2} = I_{D1} - I_{D2}$$

(2.2)

Le courant de sortie obtenu pour une tension d'entrée  $\Delta V = V_{in1} - V_{in2}$ :

$$I_{o} = \begin{cases} \Delta V \sqrt{2I_{p}\beta} \sqrt{1 - \frac{\beta}{2I_{p}}} (\Delta V)^{2} & \text{pour} & |\Delta V| \leq \sqrt{\frac{I_{p}}{\beta}} \\ I_{p} \text{ sign}(\Delta V) & \text{pour} & |\Delta V| > \sqrt{\frac{I_{p}}{\beta}} \end{cases}$$

$$(2.3)$$

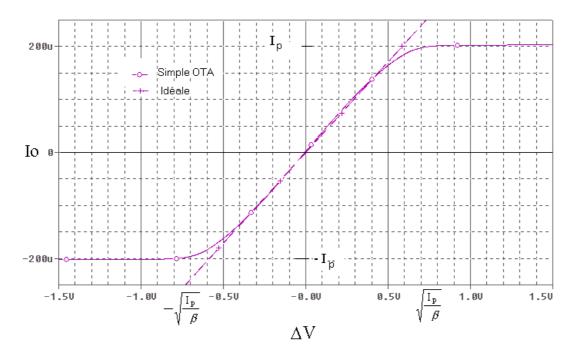

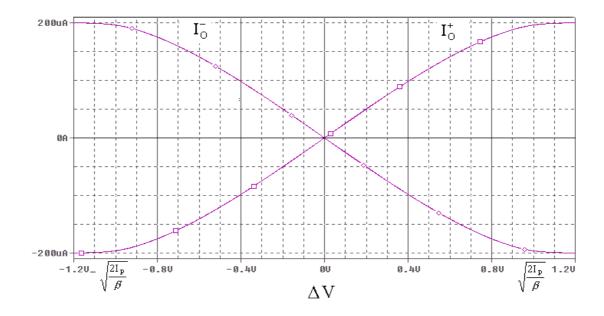

La tension maximale nécessaire pour le fonctionnement de la paire de source couplée  $(M_1 \text{ et } M_2) \text{ opérant dans la régions de saturation, est donnée par } \sqrt{\frac{I_P}{\beta}} \text{ , par exemple}$   $pour \left(\frac{W}{L}\right)_{M1,M2} = \frac{50\mu}{6\mu} \text{ et } I_P = 200\mu\text{A, on trouve la plage de fonctionnement théorique}$   $\sqrt{\frac{I_P}{\beta}} = 614.3\text{mV, ceci est montré sur la figure 2.3.}$

Figure 2.3: Courant de sortie de l'OTA à sortie unique en fonction de la tension d'entrée.

#### 2.3.1 Linéarité

La linéarité obtenue par la méthode du courant de sortie de l'OTA en fonction de la tension d'entrée, ce qui donne la transconductance non linéaire d'après l'équation (2.3)[1], sur l'intervalle de tension qui assure le fonctionnement de l'OTA.

$$G_{m} = \frac{\partial I_{0}}{\partial \Delta V} = \frac{\sqrt{2I_{p}\beta} \left[ 1 - \frac{\beta}{I_{p}} \Delta V^{2} \right]}{\sqrt{1 - \frac{\beta}{2I_{p}} \Delta V^{2}}}$$

(2.4)

Pour pouvoir étudier la linéarité de l'OTA on fait un développement en série de l'équation (2.3). On obtient pour le courant de sortie la relation suivante :

$$I_{O} = \sqrt{2I_{P}\beta} \times \Delta V + \left(0 - \frac{1}{2\sqrt{2}} \times \frac{\beta^{\frac{3}{2}}}{\sqrt{I_{P}}} \times \Delta V^{3} + 0 - \dots\right)$$

(2.5a)

$$I_{O} = a_{1} \times \Delta V + a_{2} \times \Delta V^{2} + a_{3} \times \Delta V^{3}$$

(2.5b)

La première harmonique  $a_1$  donne la transconductance ( $a_1$ =Gm), la troisième harmonique  $a_3$  est responsable de la non linéarité. Pour avoir une bonne linéarité on doit minimiser  $a_3$  par rapport à  $a_1$ . La valeur de la transconductance  $\mathrm{Gm} = \sqrt{2\mathrm{I}_\mathrm{P}\,\beta}$  est donnée pour la plage de tension  $|\Delta\mathrm{V}| < \sqrt{\mathrm{I}_\mathrm{P}\,/\,\beta}$  est représentée sur la figure 2.3. La linéarité est qualifiée comme le rapport entre la troisième harmonique  $a_3$  et la premier harmonique  $a_1$ , qui donne une condition sur les caractéristiques statiques des transistors composant l'OTA :

$$HD_3 = \frac{1}{2} \times \frac{a_3}{a_1} \times \Delta V^2 = \frac{\beta}{16I_p} \times \Delta V^2$$

(2.5c)

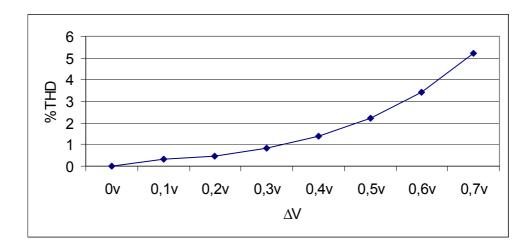

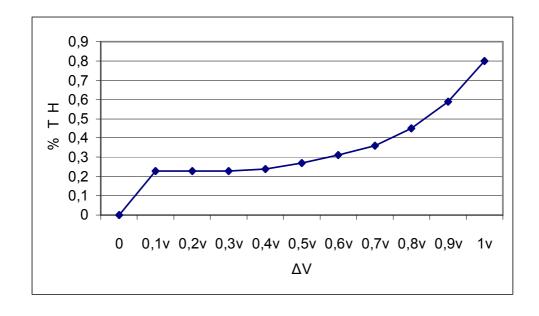

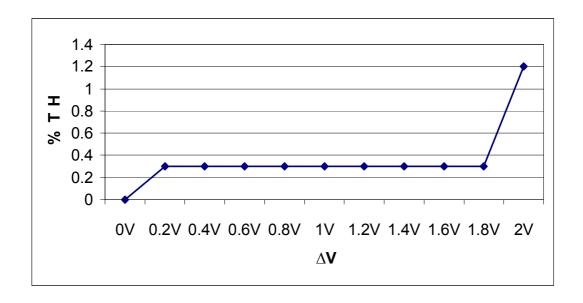

Une bonne linéarité est donnée par une minimisation de  $\beta$  qui est déterminée par les dimensions (W/L) des transistors  $M_1$  et  $M_2$ , ce qui donne une grande plage de la linéarité. La figure suivant figure 2.4 montre la non linéarité de l'OTA simple, pour  $\left(\frac{W}{L}\right)_{M_1M_2} = \frac{50\mu}{6\mu}$  et  $I_P$ =200 $\mu$ A,

Figure 2.4 : La non linéarité de transconductance sur la plage de tension d'entrée  $\Delta V$ .

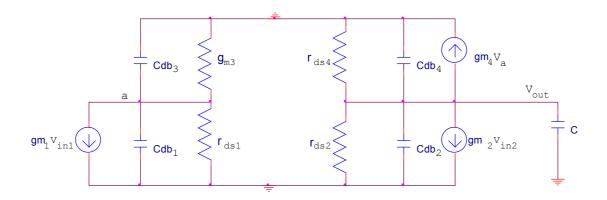

#### 2.3.2 L'étude en AC d'un OTA Simple

L'analyse AC est nécessaire pour vérifier la bande passante de l'OTA sur laquelle est branchée une capacité à la sortie de faible valeur.

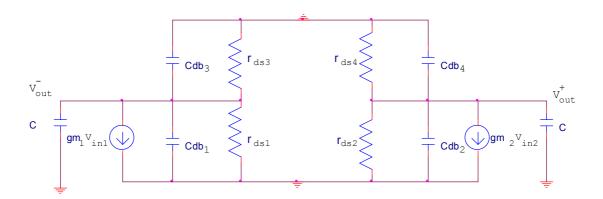

Figure 2.5 : Modèle en petit signaux de l'OTA à sortie unique.

Le modèle petit signaux pour un OTA simple à sortie unique en considérant les transistors dans la région de saturation est représenté sur la figure 2.5 [6], la tension sur la nœud (a) agit entre les transistors  $M_3$  et  $M_1$ , les résistances et capacités parallèles sur la figure 2.5 sont données par:

résistance:

$$g = \frac{1}{r_{ds2}} + \frac{1}{r_{ds4}}$$

(2.6a)

parasité Capacité:

$$C_P = C_{db4} + C_{db2}$$

(2.6b)

la transconductance:

$$Gm = gm_1 = gm_2$$

(2.6c)

où la tension différentielle d'entrée est  $V_{in}$  = $V_{in1}$ - $V_{in2}$ . La fonction de transfert de cette simple OTA:

$$H(s) = \frac{V_{\text{out}}}{V_{\text{in}}} = \frac{Gm}{g + s(C_P + C)}$$

(2.7)

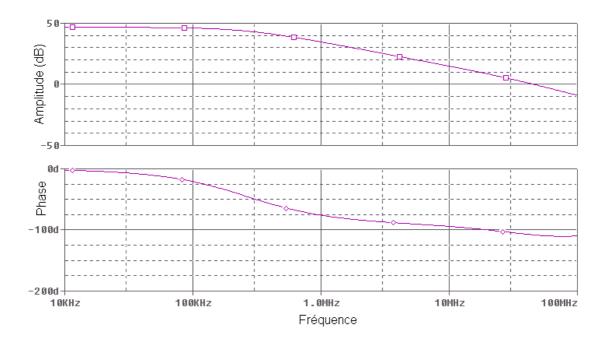

Pour une grande impédance de sortie g et une capacité faible  $C_P$ , on donne un intégrateur, qui est plus proche de  $H(s) = \frac{Gm}{C\,s}$  de l'OTA idéale, pour cela il faut donnée une dimension des transistors  $M_3$  et  $M_4$  minimum par rapport à  $M_1$  et  $M_2$ . Pour  $\left(\frac{W}{L}\right)_{M1,M2} = \frac{50\mu}{6\mu}$ ,  $\left(\frac{W}{L}\right)_{M3,M4} = \frac{10\mu}{6\mu}$  et une capacité de sortie C = 1pf avec un courant de polarisation  $I_P = 200\mu A$ , on obtient par simulation le gain  $A_{dB} = H(0) = \frac{Gm}{g} = 46.7$ db et la fréquence de coupure  $f = \frac{g}{2\pi(C_P + C)} \approx 466$ khz. Les résultats de simulations donnée sur la figure 2.6 montre que l'OTA n'est pas tout a fait un intégrateur idéal ceci est du à l'effet interne de l'OTA (la résistance g et la capacité parasité  $C_P$ ).

Figure 2.6 : La fonction de transfert de l' OTA à sortie unique.

#### 2.3.3 Linéarité par variation sur la structure de l'étage d'entrée

Figure 2.7 : Amplificateur opérationnel de transconductance avec un nouvel étage d'entrée.

Cet étage d'entrée est construit à partir de deux étages d'entrées différentiels simples entrecroisés. Quelques ajouts demeurent nécessaires afin de contrôler la transconductance avec source de courant sur chaque étage, on obtient le circuit représenté à la figure 2.7 [1]. Rappelons d'abord que cet étage représente une évaluation d'une architecteur ou l'on désirait améliorer la non linéarité, cette méthode de croisement fait une différence de deux courants de chaque cellule qui est déjà donné par l'équation (2.3), et qui donne une nouvelle formule du courant de sortie donnée par l'équation (2.8). Pour un courant de polarisation I<sub>P1</sub>>I<sub>P2</sub>, on trouve la formule suivante pour une plage de tension d'entrée ΔV:

$$I_{O} = \Delta V \sqrt{2I_{P1}\beta_{1}} \sqrt{1 - \frac{\beta_{1}}{2I_{P1}} \Delta V^{2}} - \Delta V \sqrt{2I_{P2}\beta_{2}} \sqrt{1 - \frac{\beta_{2}}{2I_{P2}} \Delta V^{2}}$$

$$pour \quad |\Delta V| \le \sqrt{\frac{I_{P2}}{\beta_{2}}}$$

(2.8)

Pour une condition sur  $\beta_1 \neq \beta_2$  et  $I_{P1} \neq I_{P2}$ , on ne néglige pas la transconductance pour une faible tension d'entrée, donc on trouve la formule suivante :

$$I_{O} = \left(\sqrt{2I_{P1}\beta_{1}} \Delta V - \frac{1}{2\sqrt{2}} \times \frac{\beta_{1}^{\frac{3}{2}}}{\sqrt{I_{P1}}} \Delta V^{3}\right) - \left(\sqrt{2I_{P2}\beta_{2}} \Delta V - \frac{1}{2\sqrt{2}} \times \frac{\beta_{2}^{\frac{3}{2}}}{\sqrt{I_{P2}}} \Delta V^{3}\right) (2.9a)$$

$$I_{O} = \left(\sqrt{2I_{P1}\beta_{1}} - \sqrt{2I_{P2}\beta_{2}}\right)\Delta V - \left(\frac{1}{2\sqrt{2}} \times \frac{\beta_{1}^{\frac{3}{2}}}{\sqrt{I_{P1}}} - \frac{1}{2\sqrt{2}} \times \frac{\beta_{2}^{\frac{3}{2}}}{\sqrt{I_{P2}}}\right)\Delta V^{3}$$

(2.9b)

Pour le terme du troisième ordre de l'équation (2.9) c'est la même valeur obtenue pour la distorsion harmonique maximum (équation 1.13) qu'on doit éliminer pour obtenir une bonne linéarité, donc on trouve alors la condition sur la dimension des transistors MOS de cette cellule qui est montrée par l'équation (2.10) :

$$\left[\frac{\left(\frac{W}{L}\right)_{1}}{\left(\frac{W}{L}\right)_{2}}\right]^{3/2} = \left[\frac{I_{P_{1}}}{I_{P_{2}}}\right]^{1/2}$$

(2.10)

La transconductance linéaire est donnée par la différence entre la transconductance de deux cellules mais pour une faible tension d'entrée:

$$Gm = Gm_1 - Gm_2 = \sqrt{2I_{P1} \beta_1} - \sqrt{2I_{P2} \beta_2}$$

(2.11)

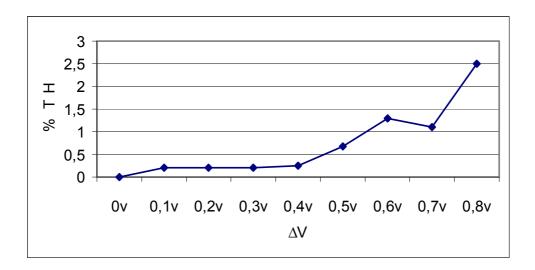

La non-linéarité de transconductance est montrée sur la figure 2.8 suivante, pour  $I_{P1}=200\mu A$  et  $I_{P2}=100\mu A$  avec  $\left(\frac{W}{L}\right)_1=\frac{50\mu}{6\mu}$  et  $\left(\frac{W}{L}\right)_2=\frac{40\mu}{6\mu}$ .

Figure 2.8: La non linéarité de transconductance en fonction de la plage de tension d'entrée  $\Delta V$ .

#### 2.3.4 Linéarité par variation du courant de polarisation

Pour avoir une performance sur la linéarité pour un OTA simple de la figure 2.2 on propose un circuit qui permet de varier le courant de polarisation en fonction de la tension d'entrée selon la relation suivante :

$$I_{P}=I'_{P}+\beta' \Delta V^{2} \tag{2.12}$$

Soit l'équation 2.12 dans l'équation 2.3 on obtient la relation suivante:

$$I_{o} = \begin{cases} \Delta V \sqrt{2I_{P}'\beta} \sqrt{1 - \frac{\beta - 2\beta'}{2I_{P}'}} \Delta V^{2} & \text{pour} & |\Delta V| \leq \sqrt{\frac{2I_{P}'}{\beta}} \\ I_{P}' + \beta' \Delta V^{2} & \text{pour} & |\Delta V| > \sqrt{\frac{2I_{P}'}{\beta}} \end{cases}$$

$$(2.13)$$

On obtient une transconductance linéaire  $Gm = \sqrt{2I_P'\beta}$  pour  $\beta' = \beta/2$ , où le circuit qui génère ce courant de polarisation, est montré dans la figure 2.9 [1,5].

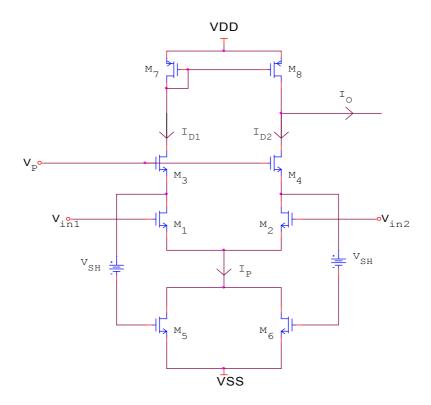

Figure 2.9 : Amplificateur opérationnel de transconductance polarisé par un courant variant en fonction de la tensions d'entrée.

Ce nouvel amplificateur contient une cellule différentielle présentée par six transistors  $M_1$ - $M_6$  comme montré sur la figure 2.9, ou chaque drain est liée par l'autre source, les transistors  $M_1$  et  $M_2$  permettent la conversion tension-courant qui est la sortie sur chaque branche de  $M_3$  et  $M_4$ . La cellule  $M_1$  et  $M_2$  polarisée par le courant Ip qui est généré par les transistors  $M_5$  et  $M_6$  à partir de la copie de la différence de la tension d'entrée  $\Delta V$  aux grilles de  $M_5$  et  $M_6$  en série avec à la tension de conduite  $V_{SH}$  sur la figure 2.9, les résultats donnés pour la tension grille-source de  $M_5$  et  $M_6$  est:

$$V_{GSS} = V_{CM} - \frac{\Delta V}{2} \tag{2.14a}$$

$$V_{GS6} = V_{CM} + \frac{\Delta V}{2} \tag{2.14b}$$

Où:

$$V_{CM} = \frac{V_P - V_{SH} - V_{SS}}{2} \tag{2.15}$$

$V_p$ : La tension de polarisation sur la grille de  $M_3$  et  $M_4$  ( $V_p > V_{SH} + V_{SS}$ ) donc en sommant les courants de draine de  $M_5$  et  $M_6$  on trouve le nouveaux courant de polarisation :

$$I_{P} = I_{D5} + I_{D6} = 2\beta_{5.6}(V_{CM} - V_{T})^{2} + \beta_{5.6}\Delta V^{2}$$

(2.16)

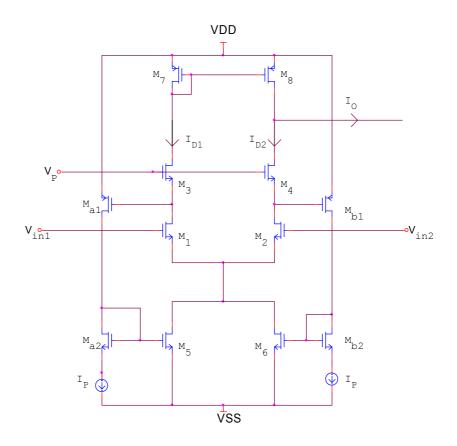

Alors l'équation (2.16) est la même que celle de (2.12) pour  $\beta' = \beta_{5,6}$  et  $I_P' = 2\beta_{5,6} (V_{CM} - V_T)^2$ , ce qui donne une transconductance linéaire pour une grande plage de tension d'entrée par rapport à l'OTA. Les sources de tension flottantes  $V_{SH}$  peuvent être réalisées par une paire de transistor MOS double dont l'un est relié comme une diode, polarisé par un courant  $I_P$  comme représenté sur la figure 2.10 par les transistors  $(M_{a1}, M_{a2})$  et  $(M_{b1}, M_{b2})$ . La non linéarité est représentée par la figure 2.11 en fonction de la tension d'entrée, pour  $I_P$ =200 $\mu$ A et  $\left(\frac{W}{L}\right)_{MLM2} = \frac{50\mu}{6\mu}$ .

Figure 2.10: Remplacement de la tension de conduite  $V_{SH}$  de la figure 2.9 par une paire de transistor MOS.

Figure 2.11: La non linéarité de transconductance en fonction de la tension d'entrée  $\Delta V$ .

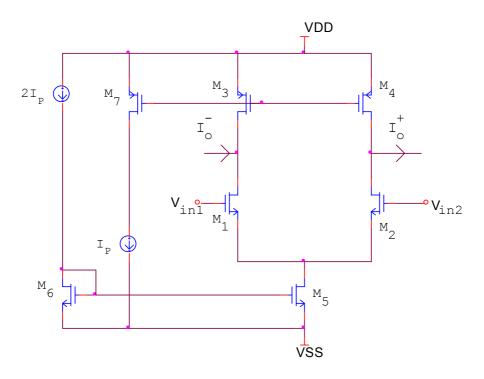

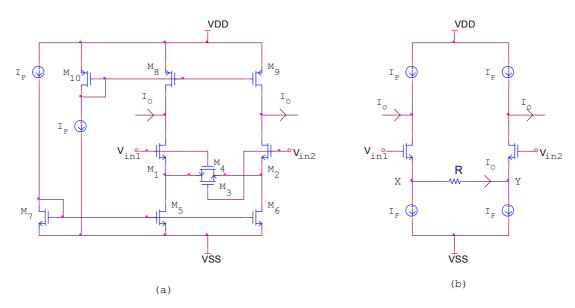

#### 2.4 AMPLIFICATEUR DIFFERENTIEL DE TRANSCONDUCTANCE

Sur la figure 2.12 est représentée une implémentation de l'amplificateur opérationnel de transconductance différentielle simple (structure de base) avec deux sortie, pour chaque demi-circuit, le premier demi-circuit est réalisé par les transistors MOS  $M_1$  et  $M_3$ , le deuxième par  $M_2$  et  $M_4$ .Les deux demi-circuit sont polarisés par la branche qui contient le transistor  $M_7$  et le courant de polarisation Ip. La paire de source couplée est polarisée par un circuit qui contient les transistors  $M_5$  et  $M_6$  et par un courant de polarisation 2Ip. Pour les signaux de tension d'entrée  $V_{in1}$  et  $V_{in2}$  on obtient un courant de sortie sur chaque demi-circuit  $I_0^+$  et  $I_0^-$  [6,7].

Figure 2.12 : Amplificateur différentiel de transconductance simple.

Le sujet de cette section est d'obtenir une transconductance différentielle linéaire. Pour ce type d'amplificateur l'étude en DC conduit aux équations suivantes où les courants de drains des transistors  $M_1$  et  $M_2$  sont dans leur région de saturation  $|\Delta V| < (2Ip/\beta)^{1/2}$ :-

$$I_{D1} = I_{P} + \beta \Delta V \sqrt{\frac{I_{P}}{\beta} - \left(\frac{\Delta V}{2}\right)^{2}}$$

(2.17a)

$$I_{D2} = I_{P} - \beta \Delta V \sqrt{\frac{I_{P}}{\beta} - \left(\frac{\Delta V}{2}\right)^{2}}$$

(2.17b)

Le courant de sortie est donné par:

$$I_{O}^{+} = I_{D1} - I_{P}^{-} = \sqrt{\beta I_{P}} \sqrt{1 - \frac{\beta}{I_{P}} \left(\frac{\Delta V}{2}\right)^{2}} \Delta V$$

(2.18a)

$$I_{O}^{-} = I_{D2} - I_{P}^{-} = -\sqrt{\beta I_{P}} \sqrt{1 - \frac{\beta}{I_{P}} \left(\frac{\Delta V}{2}\right)^{2}} \Delta V$$

(2.18b)

Donc les courants de sortie sur chaque branche en fonction de la tension sont représentés sur la figure suivante, pour  $I_P=200\mu A$  et  $\left(\frac{W}{L}\right)_{M1M2}=\frac{50\mu}{6\mu}$ :

Figure 2.13 : Les courants de sortie sur chaque branche  $I_O^+$  et  $I_O^-$  , par variation de la tension d'entrée.

On obtient la transconductance différentielle des deux sorties en courant avec des signes opposés (équation 2.19).

$$Gm^{+} = \left| Gm^{-} \right| = \frac{\sqrt{I_{p}\beta} \left[ 1 - \frac{\beta}{2I_{p}} \Delta V^{2} \right]}{\sqrt{1 - \frac{\beta}{I_{p}} \left( \frac{\Delta V}{4} \right)^{2}}}$$

(2.19)

#### 2.4.1 Etude en AC

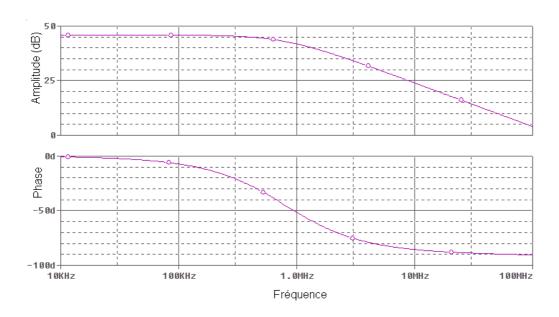

le modèle de l'OTA différentiel en AC est représenté sur la figure 2.14, en ajoutant un condensateur C entre les noeuds de sorties,  $V_{out}^+$  et  $V_{out}^-$  [7].

Figure 2.14 : Modèle petit signal équivalent du circuit de la figure 2.14.

A partir de simplification donnant les équivalences entre les capacités parallèles et les résistances parallèles on obtient:

$$g_{o} = \frac{1}{r_{ds1}} + \frac{1}{r_{ds3}}$$

(2.20a)

$$Cp = C_{db1} + C_{db3}$$

(2.20b)

Donc on trouve les équations entre l'entrée et sortie sur chaque branche de la figure 2.14 :

$$-gm_1 V_{in1} = (go + s(Cp + C)) V_{out}^-$$

(2.21a)

$$-gm_2 V_{in2} = (go + s(Cp + C)) V_{out}^+$$

(2.21b)

La différence entre ces deux équations, permet d'obtenir la fonction de transfert :

$$\frac{V_{\text{out}}}{V_{\text{in}}} = \frac{gm}{go + s(C + C_P)}$$

(2.22)

Pour  $V_{\text{out}} = V_{\text{out}}^+ - V_{\text{out}}^-$ , Le graphe de cette équation est représenté sur la figure 2.15.

Figure 2.15 : La fonction de transfert de l'OTA différentiel Simple.

Donc le gain en DC à  $G=\frac{gm_1}{go}\approx 42 db$ , et la fréquence de coupure est  $fc=\frac{go}{2\pi(Cp+2C)}=500 \text{ KHz}, \text{ La capacité de la sortie parasite Cp modifie seulement}$  la valeur effective de la capacité C, mais garde la forme de la fonction de transfert de l'intégrateur.

#### 2.4.2 Linéarisations de l'amplificateur différentiel de transconductance

Une nouvelle structure est obtenue en ajoutant sur l'amplificateur différentiel de transconductance, entre les sources de transistors  $M_1$  et  $M_2$  deux transistors MOS couplées  $M_3$  et  $M_4$  comme montré sur la figure 2.16a. Ces deux transistors  $M_3$  et  $M_4$  jouent le rôle d'une résistance, ils permettent d'améliorer la linéarité. L'architecteur simplifié montre le sens des courants montrés sur la figure 2.16b [7,8]. Ces courants sont donnés par :

Figure 2.16 : (a) Cellule différentielle de transconductance opérant dans la région ohmique (b) simplification sur la circulation de courant sur la figure (a).

$$I_{P} + I_{O} = \beta (V_{in1} - V_{X} - V_{T})^{2}$$

(2.23a)

$$I_{P} - I_{O} = \beta (V_{in2} - V_{Y} - V_{T})^{2}$$

(2.23b)

$$V_X - V_Y = R \times I_O \tag{2.23c}$$

$V_X$  et  $V_Y$  sont des tensions entre les bornes de la résist\*nce (figure 2.16 (b)), donc on obtient les équations de tension d'entrée :

$$V_{\text{in 1}} = \sqrt{\frac{I_p}{\beta}} \times \sqrt{1 + \frac{I_o}{I_p}} + V_X$$

(2.24a)

$$V_{in 2} = \sqrt{\frac{I_p}{\beta}} \times \sqrt{1 - \frac{I_O}{I_p}} + V_Y$$

(2.24b)

$$Veff = \sqrt{\frac{I_p}{\beta}} = Cst$$

(2.24c)

Par la différence entre (2.24a) et (2.24b) on trouve la relation entre la tension d'entrée et le courant de sortie:

$$\Delta V = V_{\text{in 1}} - V_{\text{in 2}} = Veff \left( \sqrt{1 + \frac{I_{\text{O}}}{I_{\text{P}}}} - \sqrt{1 - \frac{I_{\text{O}}}{I_{\text{P}}}} \right) + R I_{\text{O}}$$

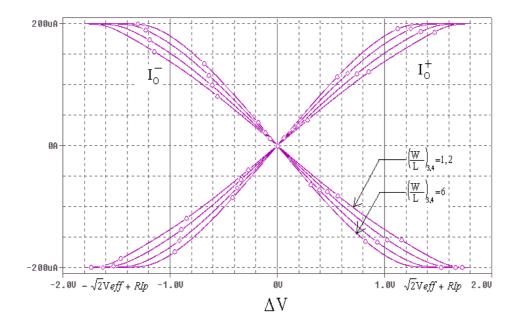

(2.25)

Pour  $\Delta V=0$  donc  $I_O=0$ , on est limité par  $\Delta V \leq \left(\sqrt{2} V \textit{eff} + R \ I_P\right)$  pour  $I_O=I_P$ , donc on obtient une grande plage de transconductance par une augmentation sur la valeur de R, on trouve les sortie en courants qui sont représenté par la figure 2.17 en fonction des dimensions W/L des transistors  $M_3$  et  $M_4$ , pour  $I_P=200\mu A$  et  $\left(\frac{W}{L}\right)_{M_1,M_2}=\frac{50\mu}{6\mu}$ .

Figure 2.17 : Les courants de sortie par rapport à la tension d'entrée  $\Delta V$ , pour chaque variation sur la dimension W/L de  $M_3$  et  $M_4$ .

Pour avoir la formule de transconductance à partir de l'équation 2.25 on fait un développement, par la série de Maclaurin, pour obtenir la condition de linéarité.

$$\frac{\Delta V}{Veff} = \frac{I_{p.R}}{Veff} \cdot \frac{I_{o}}{I_{p}} + \left(\sqrt{1 + \frac{I_{o}}{I_{p}}} - \sqrt{1 - \frac{I_{o}}{I_{p}}}\right) \\

= \left(1 + \frac{I_{p.R}}{Veff}\right) \cdot \frac{I_{o}}{I_{p}} + \frac{1}{8} \cdot \left(\frac{I_{o}}{I_{p}}\right)^{3} + \dots$$

(2.26)

Alors le troisième distorsion harmonique est donné par:

$$HD_{3} = \frac{1}{8 \cdot \left(1 + \frac{I_{p} \cdot R}{Veff}\right)} \left(\frac{I_{o}}{I_{p}}\right)^{2}$$

$$(2.27)$$

Pour minimiser la troisième distorsion harmonique  $HD_3$ , il faut avoir une grande valeur de résistance, par applications de cette condition on trouve que

la transconductance obtenue par la première distorsion harmonique (le terme linéaire) est:

$$Gm^{+} = \left| Gm^{-} \right| = \frac{I_{O}}{\Delta V} = \frac{I_{P}}{Veff \left( 1 + \frac{I_{P} \cdot R}{Veff} \right)} = \frac{\sqrt{\beta \cdot I_{P}}}{1 + R \cdot \sqrt{\beta \cdot I_{P}}}$$

(2.28)

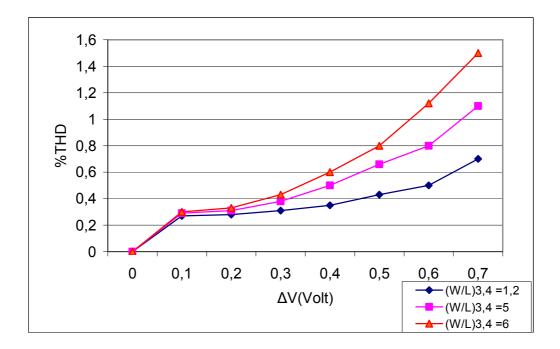

Sur la figure suivante est représentée, la non linéarité de la transconductance à partir de la variation de la résistance R, qui est donnée par la variation des dimensions W/L de  $M_{3,4}$  sur l'intervalle [1.2,6] .On obtient une grande linéarité pour une dimension  $\left(\frac{W}{L}\right)_{3,4}$  minimum (une grande valeur de résistance).

Figure 2.18 : La variation de la non linéarité de transconductance en fonction de la tension d'entrée pour chaque dimension W/L de M<sub>3</sub> et M<sub>4</sub>.

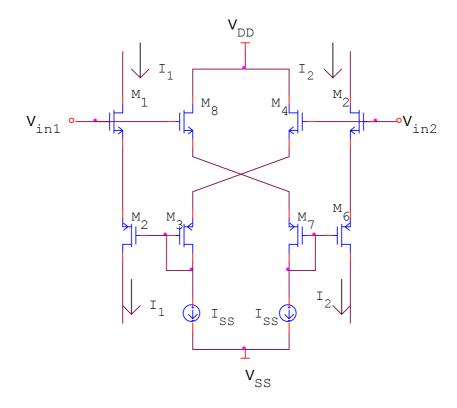

## 2.5 AMPLIFICATEUR DIFFERENTIEL DE TRANSCONDUCTANCE AVEC QUATRE ENTREES

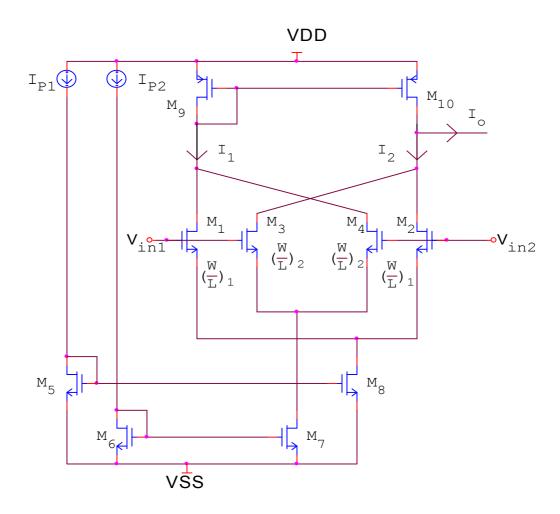

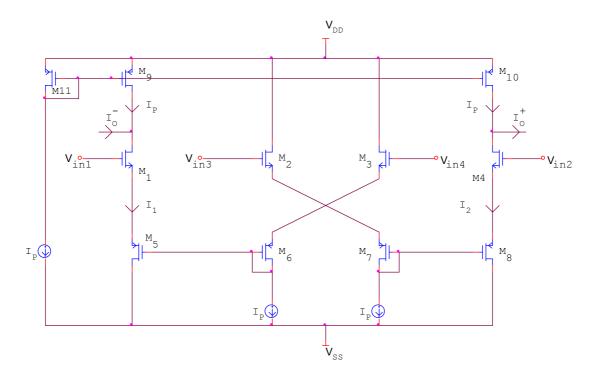

L'utilisations par une double structure d'OTA de sortie unique ou d'une transconductance différentielle permet d'obtenir un OTA avec quatre entrées et deux ou quatres sorties [10]. Mais il y'a une nouvelle architecture simple basée sur la méthode de transconductance en classe AB représentée sur la figure 2.19 qui utilise deux ou quatre entrées selon le type d'utilisation [9,10].

Figure 2.19 : Transconductance en Classe AB avec quatre entrées et double sortie.

Les différents courants de sortie sont dérivés à partir des équations de la double paire CMOS ( $\beta_{eq} = \beta_n // \beta_p$ ), autour des transistors  $M_1, M_5, M_6, M_3$  et  $M_4, M_8, M_7$  et  $M_2$ , respectivement:

$$V_{in1} - V_{in4} = \sqrt{\frac{I_p}{\beta_{eq}}} - \sqrt{\frac{I_1}{\beta_{eq}}}$$

(2.29a)

$$V_{in2} - V_{in3} = \sqrt{\frac{I_p}{\beta_{eq}}} - \sqrt{\frac{I_2}{\beta_{eq}}}$$

(2.29b)

Ces deux équations donnés dans la région de saturation des transistors :

$$|\Delta V| \le \sqrt{\frac{I_P}{\beta_{eq}}}$$

(2.29c)

Donc:

$$I_{1} = I_{P} + \beta_{eq} \cdot (V_{in1} - V_{in4})^{2} + 2\sqrt{I_{P}\beta_{eq}} \cdot (V_{in1} - V_{in4})$$

(2.30a)

$$I_{2} = I_{P} + \beta_{eq} \cdot (V_{in2} - V_{in3})^{2} - 2\sqrt{I_{P}\beta_{eq}} \cdot (V_{in2} - V_{in3})$$

(2.30b)

Alors par soustraction de courant I<sub>P</sub> sur chaque branche de M<sub>9</sub> et M<sub>10</sub> (figure 2.19), la sortie de courant sur le coté positive et négative de la figure 2.19 est donné par:

$$I_{O}^{+} = I_{2} - I_{P} = \left[ \beta_{eq} \cdot (V_{in2} - V_{in3}) - 2\sqrt{I_{P}\beta_{eq}} \right] \cdot (V_{in2} - V_{in3})$$

(2.31a)

$$I_{O}^{-} = I_{1} - I_{P} = \left[\beta_{eq} \cdot (V_{in1} - V_{in4}) + 2\sqrt{I_{P}\beta_{eq}}\right] \cdot (V_{in1} - V_{in4})$$

(2.31b)

Ce qui donne la formule de la transconductance non linéaire sur chaque sortie:

$$Gm^{+} = |Gm^{-}| = 2\beta_{eq} \cdot \Delta V - 2\sqrt{I_{P}\beta_{eq}}$$

(2.32)

en utilisant la condition de saturation de l'équation (2.29c) on obtient une performance sur la linéarité pour une faible tension d'entrée  $Gm \approx 2\sqrt{I_P \beta_{eq}}$ .

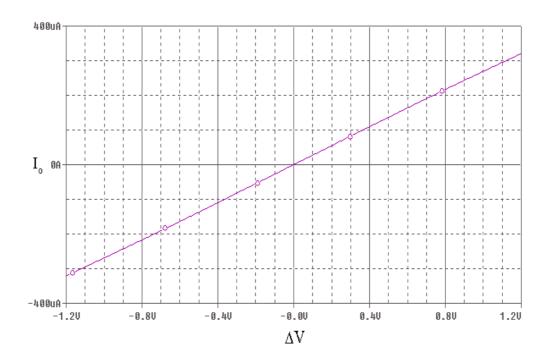

A partir de la soustraction des courants  $I_0^+$  et  $I_0^-$  on obtient:

$$I_{O} = I_{O}^{+} - I_{O}^{-} = 2\sqrt{I_{P}\beta_{eq}} \cdot [(V_{in1} - V_{in4}) - (V_{in2} - V_{in3})]$$

(2.33)

Donc on a obtenu une même valeur de transconductance sur les deux sorties en courants de valeur linéaires.

$$Gm = 2\sqrt{I_{P}\beta_{eq}}$$

(2.34)

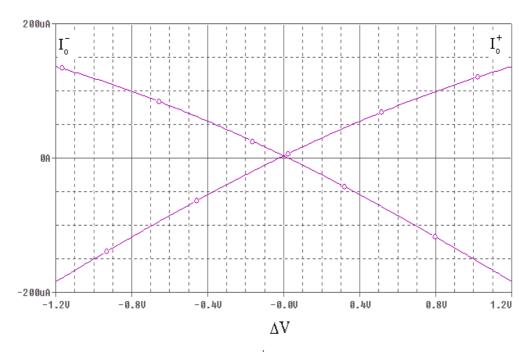

Avec cette OTA à quatre entrées on peut réaliser une double entrée pour  $\Delta V = \left(V_{in1} - V_{in2}\right) = \left(V_{in3} - V_{in4}\right) \text{remplacée dans l'équation} \quad (2.31a) \text{ et } (2.31b) \text{ qui permet d'obtenir une transconductance avec plus de performance de linéarité, de valeur } Gm = 4\sqrt{I_{\rm p}\,\beta_{\rm eq}} \text{ . par cette méthode on donne une réalisation générale donnée par le circuit représenté sur la figure 2.19. Leur transconductance } Gm = 4\sqrt{I_{\rm p}\,\beta_{\rm eq}} \text{ pour une double entrée, et } Gm = 2\sqrt{I_{\rm p}\,\beta_{\rm eq}} \text{ pour quatre entrées.}$

Pour  $\left(\frac{W}{L}\right) = \frac{50\mu}{6\mu}$  et I<sub>P</sub>=400 $\mu$ A on trouve les résultats de simulation montrés sur les

figures 2.20 et 2.21 qui expriment respectivement les équations (2.31) et (2.33). La linéarité de transconductance est montrée sur la figure 2.22, qui est donnée sur l'intervalle de saturation  $\Delta V < 2V$ .

Figure 2.20: Les courants de sortie  $I_o^+$  et  $I_o^-$ , par variation de la tension d'entrée  $\Delta V$ .

Figure 2.21: Le courant  $I_0 = I_0^+ - I_0^-$ , par variation de la tension d'entrée  $\Delta V$ .

Figure 2.22 : La non linéarité de transconductance du circuit amplificateur différentiel de transconductance en classe AB en fonction de la tension d'entrée  $\Delta V$ .

#### 2.6 CONCLUSION

Au cours du présent chapitre quelques architectures d'OTA à simple sortie, à deux sorties puis à quatre entrées et deux sorties ont été présentées. Les différentes configurations ont consisté à augmenter essentiellement la linéarité.

D'abord, à partir de l'OTA simple, la linéarité a été améliorée en proposant une structure à deux étages d'entrée entrecroisée au lieu d'un seul, et une autre structure qui est polarisée par un courant en fonction de la tension d'entrée.

Une autre structure d'OTA différentielle, opérant dans la région ohmique, qui permet d'augmenter la linéarité, a été également proposée. Cet OTA est réalisé en insérant l'équivalent d'une résistance, réalisé par deux transistors CMOS, entre les sources des transistors de l'étage d'entrée d'un OTA simple.

Enfin un OTA avec quatre entrées et deux sorties qui permet d'augmenter la linéarité a été réalisé en utilisant la méthode de transconductance en classe AB.

### Chapitre 3

# Réalisation des filtres a base de la cellule Gm-C

#### 3.1 INTRODUCTION

Les techniques d'OTAs sur lesquelles sont branchées une capacité sur la sortie dont la définition équivalente est symbolisée par Gm-C sont généralement employées pour concevoir des filtres dans le domaine de petits signaux. La simulation de la résistance par l'OTA permet de réaliser des filtres de type Gm-C ou OTA-C, équivalent aux filtres passifs. L'OTA avec plusieurs entrées et sorties permet d'obtenir des filtres plus performants, que celui de l'OTA simple.

#### 3.2 CARACTERISTIQUE DE L'INTEGRATEUR Gm -C

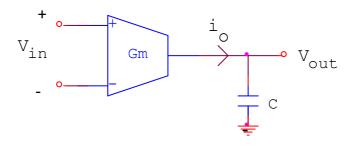

Essentiellement, le rôle de la cellule Gm est de convertir la tension appliquée à ses bornes d'entrée en courant proportionnel à la valeur de sa transconductance. Pour obtenir un intégrateur, il suffit d'y ajouter une charge capacitive à sa sortie [7,11]. On obtient alors le circuit présenté à la figure 3.1.

Figure 3.1 : Simple intégrateur Gm-C.

Si tout le courant généré par la cellule Gm se dirige vers la capacité C, ce qui donne une tension entre la borne de capacité c'est-à-dire si la tension  $V_{out}$ , alors la fonction de transfert de l'intégrateur tel que démontrée par les équations (3.1) est :

$$i_{out}(s) = Gm \times V_{in}(s)$$

(3.1a)

$$V_{out}(s) = \frac{io}{sC} = \frac{Gm}{sC} V_{in}(s)$$

(3.1b)

$$\frac{V_{\text{out}}(s)}{V_{\text{in}}(s)} = \frac{Gm}{sC}$$

(3.1c)

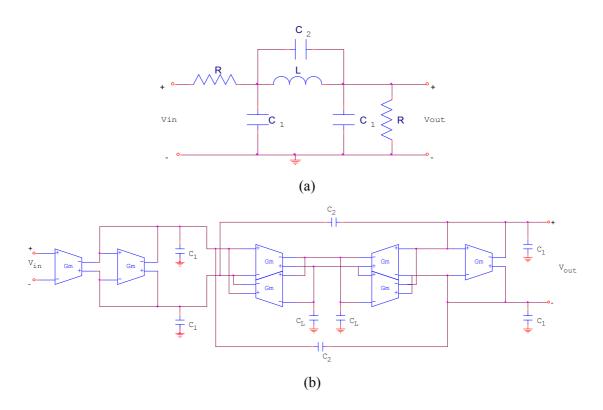

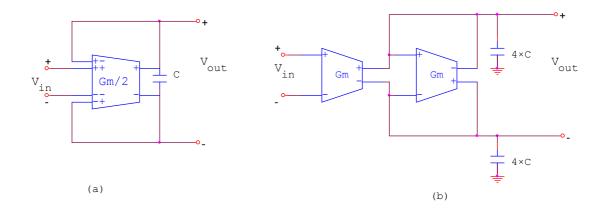

Il y a d'autres réalisations d'intégrateur Gm-C présentée sur la figure 3.2, réalisée à partir d'OTA différentielle. Sur la figure 3.2 est montrée deux réalisations différentes d'un intégrateur différentiel, bien que le circuit (figure 3.2 (b)) a quatre fois la valeur de capacité que l'autre, cette façons de relier les capacités donne une sortie en courant positive et négative qui génère deux tensions  $V_{out}^+$  et  $V_{out}^-$  [4,7,11], quoi que les deux circuits donnés ont la même formule de l'intégrateur, ceci à partir de l'étude sur le courant pour chaque figure.

Figure 3.2 : Intégrateur différentiel réalisé par la cellule de transconductance différentielle Gm.

• Sur la figure 3.2a on trouve :

$$V_{out} = \frac{i_o^+}{sC} = \frac{|i_o^-|}{sC} = \frac{Gm}{sC} V_{in}$$

(3.2)

• Sur la figure 3.2b on trouve :

$$i_{O}^{+}(s) = +Gm \times V_{in}(s)$$

(3.3a)

$$i_{0}^{-}(s) = -Gm \times V_{in}(s)$$

(3.3b)

et la tension différentielle de sortie est :

$$V_{out} = V_{out+} - V_{out-} = \frac{i_O^+}{s2C} - \frac{i_O^-}{s2C} = \frac{Gm}{sC} V_{in}$$

(3.4)

A partir de ces équations (3.2) et (3.4) on obtient la même formule de l'intégrateur:

$$\frac{V_{\text{out}}(s)}{V_{\text{in}}(s)} = \frac{Gm}{sC}$$

(3.3e)

#### 3.3 SYNTHESE DE GYRATEUR

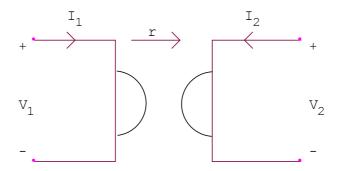

#### 3.3.1 Gyrateur

En 1948 Tellegen a présenté le gyrateur comme un élément de l'électronique idéal [11]. Un gyrateur idéal est un élément à deux ports passifs et non accordables comme représenté schématiquement sur la figure 3.3, et défini par la formule montrée dans l'équation (3.5), où r est la résistance du gyrateur.

Figure 3.3 : Symbole de gyrateur.

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} 0 - r \\ r \ 0 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

(3.5)

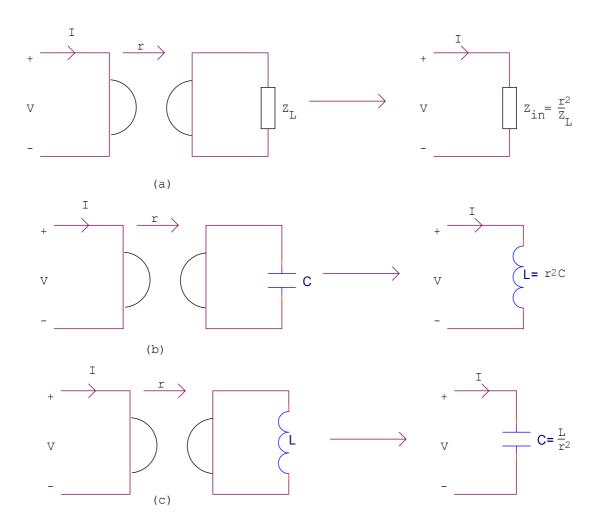

Un gyrateur Chargé par une impédance  $Z_L$  comme montré dans la figure 3.4a donne son équivalent par utilisation de l'équation (3.5), une impédance d'entrée de formule:

$$Z_{\rm in} = \frac{V_1}{I_1} = \frac{r^2}{Z_L} \tag{3.6}$$

Donc par cette méthode, on obtient l'équivalent de l'inductance par gyrateur chargé par une capacité comme montrée sur la figure 3.4b, et l'équivalent d'une capacité par un gyrateur chargé par une inductance comme montré sur la figure 3.4c.

Figure 3.4 : L'équivalent d'un gyrateur chargé par un élément passif.

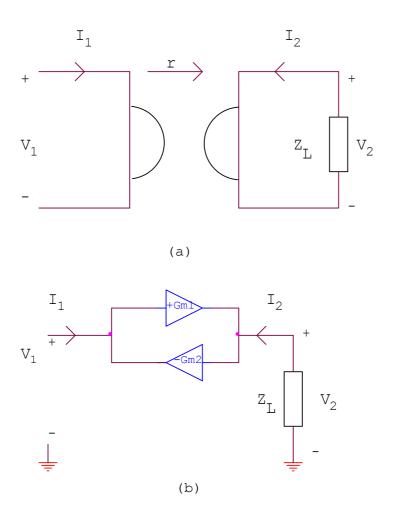

#### 3.3.2 Réalisation de gyrateur avec des transconductances

Un gyrateur réel peut être construit avec des éléments actifs tels que des op-amps ou des transconductances. Pour les filtres en haute fréquence, la réalisation de gyrateur avec des transconductances est préférable (résistance de gyrateur simulée par les transconductances) [11,12]. La réalisation du gyrateur réel figure 3.5a est donnée dans la figure 3.5b, qui est composée par deux transconductances; un avec entrée inverseuse et l'autre avec entrée non inverseuse. Les relations entre courants et tension dans la figure 3.5b sont données par:

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} 0 & -r \\ r & 0 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix} = \begin{bmatrix} 0 \\ \frac{1}{Gm_2} - \frac{1}{Gm_1} \\ 0 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

(3.7)

La formule 3.7 est donnée pour un gyrateur réel lorsque  $r=\frac{1}{Gm_1}=\frac{1}{Gm_2}$ . Mais il est nécessaire de modifier les deux transconductances  $Gm_1$  et  $Gm_2$  à partir du gyrateur dans la figure 3.5 et que le facteur  $r^2$  soit remplacé par  $\frac{Z_L}{Gm_1.Gm_2}$ . Ce modèle de gyrateur est utilisé pour la simulation de l'inductance.

Figure 3.5 : a) Modèle de gyrateur b) Réalisation de modèle gyrateur par la transconductance.

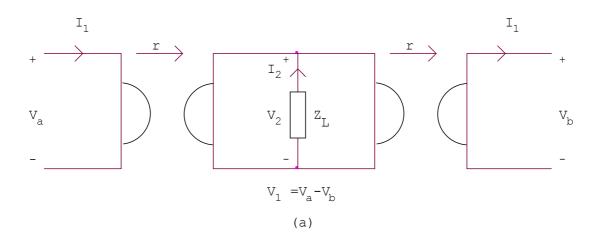

Une méthode pour mettre en application le gyrateur flottant avec deux gyrateurs est donnée par la figure 3.6a. Un gyrateur flottant est nécessaire pour la simulation des inductances flottantes. Le gyrateur flottant construit à partir de transconductance est donné par la figure 3.6b.

Figure 3.6 : a) Gyrateur flottant b) Gyrateur flottant construit par la transconductance c) L'équivalent de gyrateur flottant.

D'après la figure 3.6b on trouve les relations suivantes:

$$V_2 = -Z_L I_2 = -Z_L Gm_1 (V_b - V_a)$$

(3.8a)

$$I_1 = -Gm_2 V_2$$

(3.8b)

En combinant les relations (3.8a) et (3.8b) on obtient l'impédance d'entrée:

$$\frac{(V_a - V_b)}{I_1} = \frac{1}{Gm_1 Gm_2 Z_L}$$

(3.9a)

Donc l'équivalent de gyrateur flottant chargé par  $Z_L$  donne une impédance d'entrée de formule:

$$Z_{in} = \frac{1}{Gm_1 Gm_2 Z_L} \tag{3.9b}$$

L'équivalent d'une inductance flottante est obtenu en chargeant le gyrateur flottant par une capacité.

#### 3.3.3 Modèle du gyrateur (inductance, résistance)

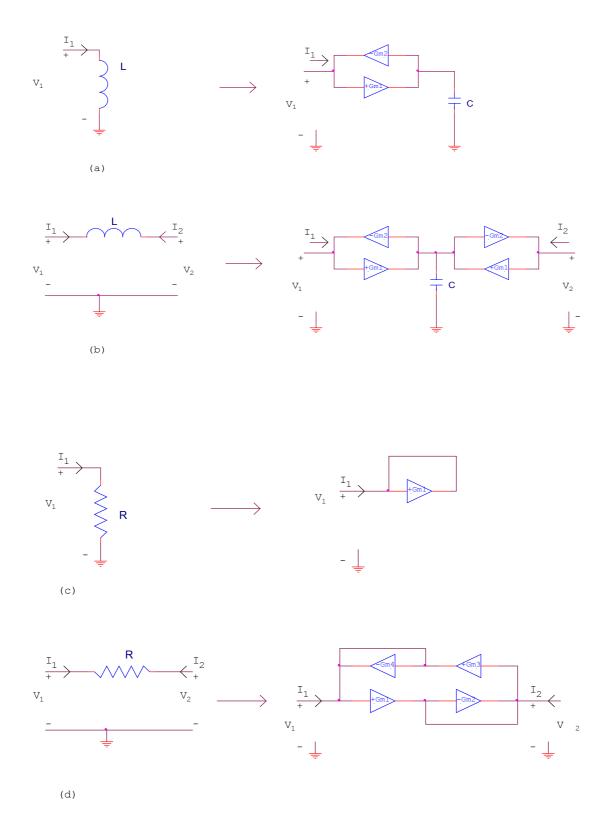

La simulation d'une résistance et d'inductance par gyrateur utilisant des OTAs est représentée par la figure 3.7 [11,12] Une résistance peut être simulée en utilisant une cellule Gm telle que montrée sur la figure 3.7c. Une résistance flottante peut être réalisée en utilisant un double suiveur de transconductance Gm<sub>1</sub> et Gm<sub>3</sub> branché respectivement par Gm<sub>2</sub> et Gm<sub>4</sub>.

Figure 3.7 : Modèle d'un gyrateur a) d'une inductance b) d'une inductance flottante

c) représentation d'une résistance d) modèle d'une résistance flottante.

La valeur de l'inductance et inductance flottante sont données par la relation suivante:

$$L = \frac{C}{Gm_1 \times Gm_2} \tag{3.10a}$$

La valeur de la résistance de son équivalent utilisant des OTAs dans la figure (3.7c) et figure (3.7d) est donnée pour la même valeur de la transconductance :

$$R = \frac{1}{-Gm_1} \tag{3.10b}$$

#### 3.4 FILTRE A GYRATEUR UTILISANT DES OTAS SIMPLES

Cette technique consiste à remplacer tous les éléments discrets d'un filtre passif tels que les résistances, condensateurs et inductances, par leurs équivalents réalisés à l'aide de cellules Gm-C [11]. En premier lieu, il faut choisir le modèle du filtre à réaliser à l'aide des éléments passifs usuels. Ces éléments sont par la suite remplacés par des cellules de transconductance simulant leurs propriétés respectives, ce qui permet de réaliser la même fonction de transfert.

#### 3.4.1 Filtre Passe bas

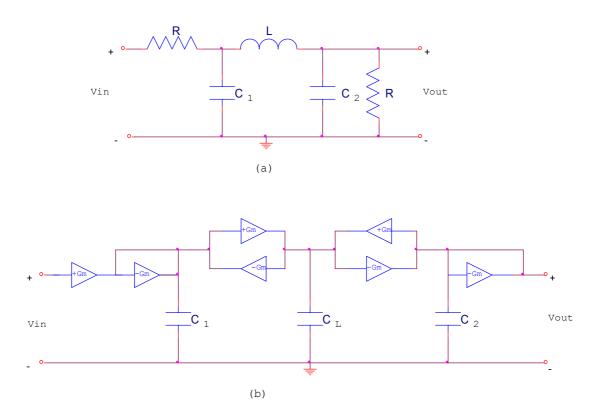

On donne un exemple de filtre passive d'ordre trois de type chebyshev représenté par un circuit RLC figure 3.8a. Pour la réalisation du filtre équivalent de type Gm-C, on remplace la résistance R et l'inductance L par leur modèle équivalent utilisant les gyrateurs à OTA. L'inductance est simulée par un gyrateur symétrique avec des transconductances Gm chargée par un condensateur  $C_L$  ou  $L=C_L/Gm^2$ , la résistance R est simulée par la transconductance 1/Gm, la représentation du filtre active est donnée par la figure 3.8b:

Figure 3.8 : Le modèle d'un filtre passe-bas à transconductance du troisième ordre du type chebyshev.

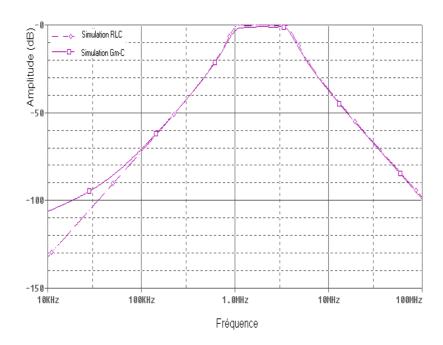

La réponse en fréquence de ce filtre obtenue par simulation en utilisant la valeur de la transconductance Gm=209uA/V et la valeur des capacités  $C_{1,2,L}=C=20pf$ , est représentée par la figure 3.9. La fréquence de coupure est donnée par

$$f_c = \frac{1}{2\pi\sqrt{LC}} = \frac{Gm}{2\pi C} = 1.66MHz$$

(3.11)

Figure 3.9 : Fonction de transfert d'un filtre passe-bas Gm-C du troisième ordre du type chebyshev.

#### 3.4.2 Filtre passe bande

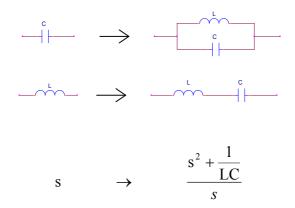

Dans cette section, on fait la conception d'un filtre passe-bande utilisant les cellules Gm, obtenu par transformation du filtre passe bas donné par la figure 3.8. La transformation d'un filtre H(s) passe bas en un filtre passe bande est obtenue en utilisant la transformation suivante:

$$s \to \frac{s^2 + \omega_o^2}{(\omega_{ch} - \omega_{cb})s} \tag{3.12a}$$

$$H(s) \Rightarrow H\left(\frac{s^2 + \omega_o^2}{(\omega_{ch} - \omega_{cb})s}\right)$$

(3.12b)

Les variables  $\omega_0$ ,  $\omega_{ch}$  et  $\omega_{cb}$  sont respectivement les fréquences centrale, de coupure basse et coupure haute du filtre passe bande.

Le résultat de transformation donne un filtre passe bande avec une large bande du sixième ordre. Le prototype de transformation représenté sur la figure 3.10 est donné en remplaçant la capacité par un circuit résonnant parallèle LC, et l'inductance par un circuit résonnant série LC. En utilisant la transformation faite sur ce filtre et en utilisant les cellules Gm. On obtient le filtre représenté par la figure 3.11.

Figure 3.10 : Les éléments de transformation LC du passe bas à passe bande.

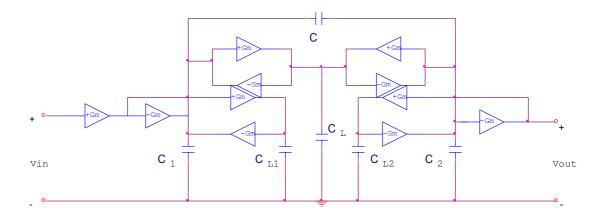

Figure 3.11: Le filtre passe bande du type chebyshev utilisant les cellules Gm.

Figure 3.12 : La Fonction de transfert du filtre passe bande à transconductance du sixième ordre du type chebyshev.

La réponse en fréquence de ce filtre obtenue par simulation en utilisant la valeur de la transconductance Gm=209uA/V et la valeur des capacités  $C_{1,2,L}=C=20pf$ , est représentée par la figure 3.12. La fréquence centrale est donnée par:

$$f_o = \frac{1}{2\pi\sqrt{LC}} = \frac{Gm}{2\pi C} = 1.66MHz$$

(3.13)

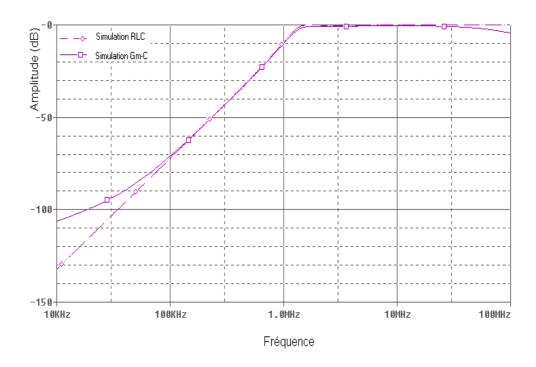

#### 3.4.3 Filtre passe haut

Le filtre passe haut est obtenu à partir du filtre passe bas (figure 3.8a) en remplaçant les capacités par les inductances et les inductances par les capacités, est puis on remplace les résistances et les inductances par leur modèle équivalent utilisant les OTAs, on obtient alors le circuit de la figure 3.13.

Figure 3.13 : Le modèle d'un filtre passe haut du type Chebyshev a base de cellule de transconductance.

Figure 3.14 : La Fonction de transfert du filtre passe haut à transconductance du type chebyshev.

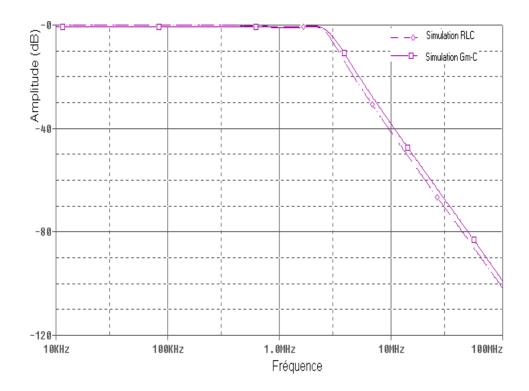

Les résultats de simulation montrent que les filtres des figures 3.8b, 3.11 et 3.13 et leurs équivalents utilisant les circuits RLC ont la même réponse en fréquence qui sont représentés respectivement par les figures 3.9, 3.12 et 3.14.

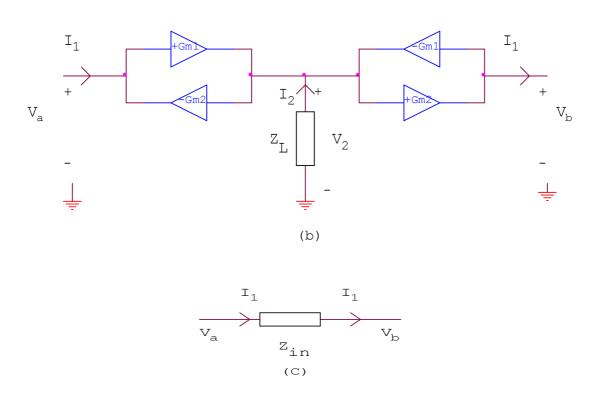

#### 3.5 FILTRE A GYRATEUR UTILISANT L'OTA DIFFERENTIEL

Un gyrateur réalisé à partir de l'OTA différentiel peut être obtenu de la même manière qu'a partir de l'OTA simple [7,13]. Ce gyrateur différentiel est représenté par la figure 3.15.

Figure 3.15 : Gyrateur différentiel réalisé par l'OTA différentiel.

Les relations entre courant et tension du gyrateur différentielles sont données par:

$$\begin{bmatrix} V_1 \\ V_2 \end{bmatrix} = \begin{bmatrix} 0 \\ \frac{1}{Gm_2} - \frac{1}{Gm_1} \\ 0 \end{bmatrix} \begin{bmatrix} I_1 \\ I_2 \end{bmatrix}$$

(3.14)

Ce modèle de gyrateur permet la réalisation symétrique d'une inductance.

La réalisation équivalente d'une résistance est donnée par la même méthode que dans le cas d'un OTA simple mais avec une structure différentielle.

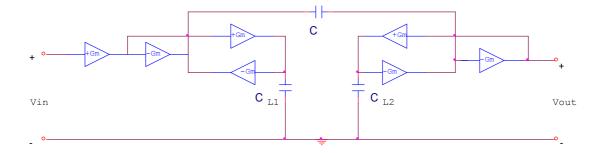

A partir du modèle du gyrateur, on obtient un filtre différentiel, on prend un exemple pour éclaircissement : un filtre elliptique passif du troisième ordre du type RLC (figure 3.16a) on donne son équivalent représenté par la figure 3.16, en utilisant l'OTA différentiel.

Figure 3.16: Filtre elliptique du troisième ordre réalisé à partir de l'OTA différentiel.

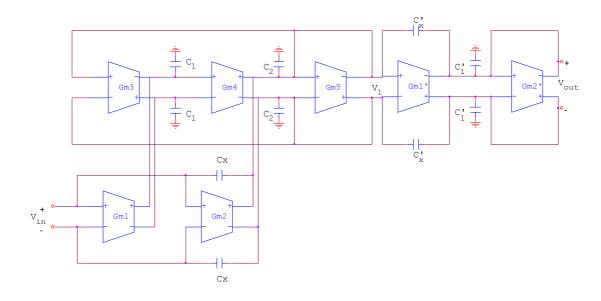

Il y a une nouvelle réalisation de l'OTA différentiel avec quatre entrées, ou son courant de sortie est donné en fonction de ces tensions d'entrée [9].

$$i_0 = \frac{Gm}{2} [(V^{++} - V^{-+}) - (V^{--} - V^{+-})]$$

(3.15)

La réalisation de l'intégrateur du type lossy [14,7,11] par cet OTA est l'équivalent de l'utilisation de deux OTAs à deux entrés et deux capacités, avec une valeur quatre fois la valeur de la transconductance et de la capacité, tel que représentées par la figure 3.18.

Figure 3.17 : Intégrateur de type lossay (filtre du premier ordre) utilisant l'OTA différentiel.

A partir de ces figures, on obtient les formules suivantes :

• pour la figure (a) on a:

$$V_{out} = \frac{i}{C_S} = \frac{Gm(V_{in} + V_{out})}{2C_S}$$

(3.16a)

$$\frac{V_{\text{out}}}{V_{\text{in}}} = \frac{1}{\frac{2C}{Gm}s - 1}$$

(3.16b)

• Pour la figure (b) on a:

$$V_{out}^{+} = \frac{Gm^{+} V_{in} - Gm^{-} V_{out}}{4Cs} = Gm \frac{V_{in} - V_{out}}{4Cs}$$

(3.17a)

$$V_{out}^{-} = \frac{Gm^{-} V_{in} - Gm^{+} V_{out}}{4Cs} = -Gm \frac{V_{in} - V_{out}}{4Cs}$$

(3.17b)

Donc par la différence entre les équations (3.17a) et (3.17b) on trouve la fonction de transfert suivante:

$$\frac{V_{\text{out}}}{V_{\text{in}}} = \frac{1}{\frac{2C}{Gm}s - 1}$$

(3.17c)

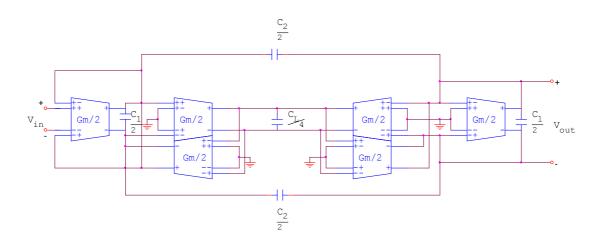

Par cette méthode, le filtre du premier ordre de la figure 3.17a est représenté sur la figure 3.18 en utilisant l'OTA à quatre entrées ce qui diminue l'utilisation du nombre d'OTA à deux entrées et le nombre des capacités [9].

Figure 3.18 : Filtre elliptique du troisième ordre réaliser à partir de l'OTA différentiel avec quatre entrée.

Pour Gm= $121\mu$ A/V et  $C_{1,2,L}$ =C=20pf en trouve la fréquence de coupure de l'équation (3.18) qui est en concordance avec les résultats obtenues par simulation de la figure 3.19.

$$f_c = \frac{1}{2\pi\sqrt{LC}} = \frac{Gm}{2\pi C} = 1MHz$$

(3.18)

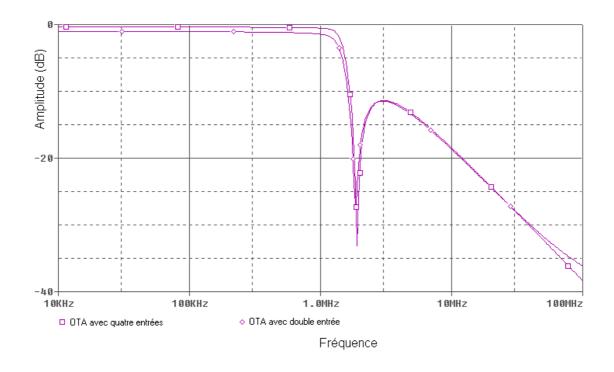

Figure 3.19 : La Fonction de transfert filtre elliptique du troisième ordre réaliser à partir de l'OTA différentiel.

La fonction de transfert du filtre elliptique de troisième ordre obtenue par simulation en utilisant l'OTA à quatre entrées et l'OTA à double entrée est représentée par la figure 3.19. On remarque que les courbes de fonction de transfert concordent, ce qui confirme de chois de l'OTA à quatre entrées.

#### 3.6 SECTION QUADRATIQUE

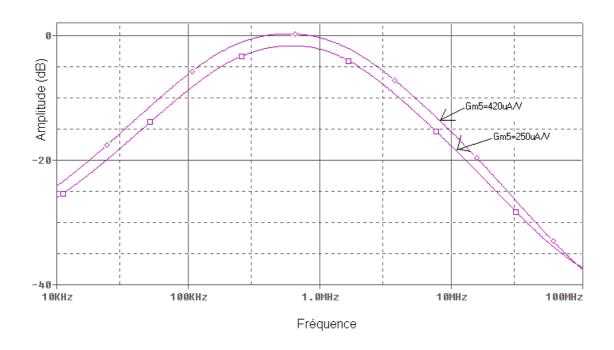

La section quadratique permet de réaliser des filtres d'ordre élevé [7] avec la possibilité de contrôler les paramètres de ces filtres. Il existe plusieurs modèles de section quadratique, la plus intéressante est celle proposée par John & Martin (1997) [4]. Elle est représentée par la figure 3.20.

Figure 3.20 : Section de filtre quadratique différentielle généralisée de John & Martin (1997).

Soit les tensions  $V_{C1}$  et  $V_{C2}$  de la figure 3.20 qui sont égales à :

$$\begin{cases} V_{C1} = (-Gm_3 \text{ Vout} + Gm_1 \text{ Vin}) \frac{1}{sC_1} \\ V_{C2} = (Gm_4 \text{ V}_{C1} + sC_x (V_{C2} - \text{Vin}) + Gm_2 \text{ Vin} - Gm_5 \text{ Vout}) \frac{1}{sC_2} \\ V_{C2} = V_{out} \end{cases}$$

(3.19)

En combinant la tension  $V_{C1}$  et  $V_{C2}$  dans l'équation (3.19) on trouve :

$$Vout\left(\frac{C_{X}}{C_{2}} + \frac{Gm_{5}}{sC_{2}} + \frac{Gm_{4}Gm_{3}}{s^{2}C_{1}C_{2}} + 1\right) = Vin\left(\frac{C_{X}}{C_{2}} + \frac{Gm_{2}}{sC_{2}} + \frac{Gm_{4}Gm_{1}}{s^{2}C_{1}C_{2}}\right)$$

(3.20)

Donc la fonction de transfert de cette section quadratique est donnée par:

$$H(s) = \frac{\left(\frac{C_{x}}{C_{x} + C_{2}}\right)s^{2} + \left(\frac{Gm_{2}}{C_{x} + C_{2}}\right)s + \frac{Gm_{1}Gm_{4}}{C_{1}(C_{x} + C_{2})}}{s^{2} + \left(\frac{Gm_{5}}{C_{x} + C_{2}}\right)s + \frac{Gm_{3}Gm_{4}}{C_{1}(C_{x} + C_{2})}}$$

(3.21)

On remarque qu'il est possible de réaliser avec ce circuit toutes les fonctions de transfert. Par exemple, si l'on désire obtenir un filtre passe-bande, il suffit d'éliminer la cellule  $Gm_1$  ainsi que le condensateur  $C_x$ . De même, on obtient un filtre passe-bas en retirant la cellule  $Gm_2$  et le condensateur  $C_x$ .

La fréquence centrale et le coefficient de qualité sont donnés par les équations suivantes:

$$\omega_o = \sqrt{\frac{Gm_3Gm_4}{C_1(C_x + C_2)}}$$

(3.22a)

$$Q = \sqrt{\frac{Gm_3Gm_4}{Gm_5^2} \left( \frac{C_x + C_2}{C_1} \right)}$$

(3.22b)

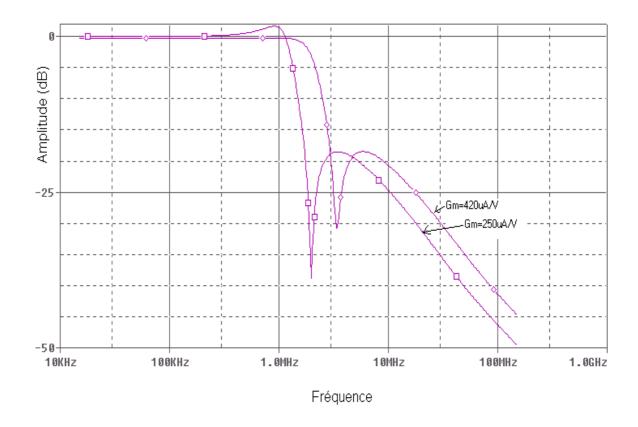

On vérifie le fonctionnement théorique de ce circuit par simulation, pour un filtre passe-bande et pour  $Gm_{2,3,4}$ =420 $\mu$ A/V, $C_{1,2}$ =40pf, avec une variation sur la largeur de bande pour  $Gm_5$ =250 $\mu$ A/V et  $Gm_5$ =420 $\mu$ A/V,on obtient les fonctions de transfert représentées par la figure 3.21.

Figure 3.21: Fonction de transfert d'un filtre passe-bande du type quadratique réaliser par la méthode John & Martin.

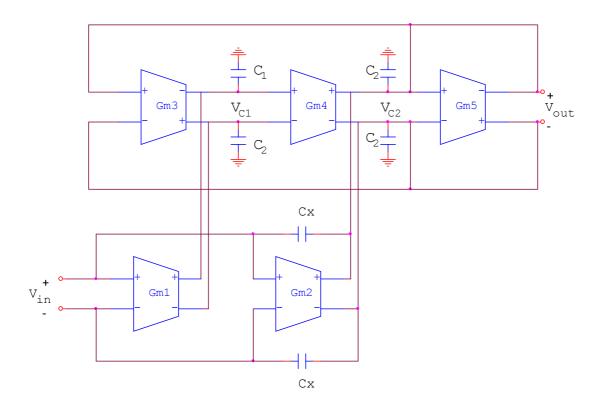

En mettant en cascade un filtre du premier ordre avec le filtre quadratique différentiel de la figure 3.21, on obtient un filtre de troisième ordre offrant plus de possibilité de contrôle de ces paramètres, représenté par la figure 3.22.

Figure 3.22: Réalisation en cascade pour obtenir un filtre du troisième ordre.

Sa fonction de transfert est donnée par:

$$H(s) = \frac{V_1}{Vin} \frac{Vout}{V_1}$$

(3.23a)

$$H(s) = \frac{\left(\frac{C_{x}}{C_{x} + C_{2}}\right)s^{2} + \left(\frac{Gm_{2}}{C_{x} + C_{2}}\right)s + \frac{Gm_{1}Gm_{4}}{C_{1}(C_{x} + C_{2})} \times \frac{\left(\frac{C_{x}'}{C_{x}' + C_{1}'}\right)s + \frac{Gm_{1}'}{C_{x}' + C_{1}'}}{s^{2} + \left(\frac{Gm_{5}}{C_{x} + C_{2}}\right)s + \frac{Gm_{3}Gm_{4}}{C_{1}(C_{x} + C_{2})} \times \frac{s + \frac{Gm_{2}'}{C_{x}' + C_{1}'}}{s + \frac{Gm_{2}'}{C_{x}' + C_{1}'}}$$

(3.23b)

Pour avoir un filtre passe bas, on doit imposer une condition sur les capacités tel que:

$$C_X = C_1 = C$$

,  $C_2 = 2C$ ,  $C_X' = 0$ , et  $C_1' = C$  pour  $C = 20p$

$$Gm_{1,3,4,5}$$

= $Gm$  ,  $Gm_{1}$ '= $Gm_{2}$ '= $Gm$  et  $Gm_{2}$ = $0\mu A/V$

Pour Gm=250  $\mu$ A/V et Gm=420  $\mu$ A/V, on obtient par simulation la fonction de transfert du filtre elliptique passe bas représenté par la figure 3.23 ce qui vérifie la fonctionnalité de ce circuit.

Figure 3.23: Fonction de transfert d'un filtre passe-bas Gm-C du troisième ordre du type elliptique réalisé par la méthode John & Martin.

#### 3.7 CONCLUSION

A partir de l'OTA on fait une réalisation d'intégrateur en ajoutant un condensateur sur la sortie. La simulation d'une résistance, et d'une inductance par les OTAs permet d'obtenir des filtres du type Gm-C par équivalence avec les filtres passifs. La transconductance différentielle permet d'obtenir un gyrateur différentiel qui permet lui aussi la réalisation des filtres différentiels. La mise en cascade de section quadratique permet d'obtenir des filtres d'ordres élevés.

## Conclusion

Ce mémoire constitue une poursuite des travaux préalablement réalisés sur les amplificateurs opérationnels de transconductance appliqués à la réalisation des filtres dans les circuits intégrés.

Au cours de ce mémoire, on trouve dans le premier chapitre, un rappel des principales architectures de la cellule de transconductance a été présenté, ainsi que les techniques pour améliorer la linéarité.

Par la suite, et dans le deuxième chapitre, plusieurs architectures de circuits amplificateurs opérationnels de transconductance ont été proposées. Les différentes configurations ont consisté à améliorer essentiellement la linéarité.

D'abord à partir de l'OTA simple la linéarité a été améliorée en proposant une structure de deux étages d'entrée entrecroisés, au lieu d'un seul, et une autre structure qui est polarisée par un courant en fonction de la tension d'entrée. Ensuite la linéarité a été améliorée en proposant un OTA différentiel opérant dans la région ohmique. Enfin la linéarité a été également augmentée en proposant un OTA avec quatre entrées et deux sorties, utilisant la méthode de transconductance en classe AB.

Dans le troisième chapitre, la résistance et l'inductance pourraient être simulées par les OTAs, ce qui permet de réaliser des filtres de type Gm-C où OTA-C par équivalence avec les filtres passifs, ainsi plusieurs configurations de filtres de type Gm-C ont été conçues, en utilisant les OTAs réalisés dans le chapitre II.

Les résultats de simulations de tous ces circuits ont montré leur bonne fonctionnalité et leur performance.

# Référence

- [1] C. Toumazou, F.J. Lidgey and D.G. Haigh, "Analog IC design: the current mode approach", London, U.K., Peter Peregrinus, 1990.

- [2] P.R. Gray and R.G. Meyer, "Analysis and design of analog integrated circuits", Third Edition. John Wiley and Sons, singapore, 1993.

- [3] G. Giustolisi, G. Plamisano, G. Palumbo, "CMRR frequency response of CMOS operational transconductance amplfiers", IEEE. Trans. Instrumentation and Measurements, Vol. 49, N°1, pp. 137-143, February 2000.

- [4] J. C. Voghell, "Réalisation de filtres analogiques Gm-C configurables dans les circuits intégrés", mémoire de maîtrise ès sciences appliquées, école polytechnique, Montréal, 2000.

- [5] S. Yan and E. Sanchez-Sinencio, "Low voltage analog Circuit Design techniques: A tutorial, IEICE. Trans. Analog Integrated Circuits and Systems", Vol. E00–A, N° 2, pp 1-17, February 2000,

- [6] T. Itakura, T. Ueno, H. Tanimoto, A. Yasuda, R. Fujimoto, T. Arai, and H. Kokatsu, "A 2.7-V, 200-kHz, 49-dBm, Stopband-IIP3, Low-Noise, Fully Balanced Gm-C Filter IC", IEEE. J. Solid-State Circuits, Vol. 34, N° 8, pp.1115-1199, August 1999.

- [7] J.E. Kardontchik,"Introduction to the design of transconductor-capacitor filters", 1992, Kluwer Academic Publishers, Boston (USA).

- [8] J.M. Stevenson, and E. S'anchez-Sinencio," An accurate quality factor tuning scheme for IF and high-Q continuous-Time filters ", IEEE. J. Solid-State Circuits, Vol.33,N° 12,pp.1970-1978, December , 1998.

- [9] P.D. Walker, and M.M. Green, "An Approach to Fully differential circuit design without common-mode feedback", IEEE. Trans. Circuits and Syst.II, Vol 43, N° 11, pp.752-762, November 1996.

- [10] R. Harjani, R. Heineke, and F. Wang, "An Integrated low voltage Class AB CMOS OTA", IEEE. J. Solid State Circuits, Vol. 34, N° 2,pp 134-141, February 1999.

- [11] B.Nauta, "Analoge cmos filters for very high frequencies", 1993, Kluwer Acadmic Publishers, Norwelle MA02061, USA.

- [12] R. L. Geiger and E. Sánchez-Sinencio, "Active filter design using operational transconductance amplifiers: A tutorial", IEEE. Circuits and Devices Magazine, Vol. 1, pp.20-32, March 1985.

- [13] W. Tan, A. Karimi-Sanjaani, A. Roithmeier, and A.A. Abidi, "A broad-Band tunable CMOS channel-select Filter for a low-IF Wireless Receiver Farbod Behbahani", IEEE. J. Solid-State Circuits, Vol.35,N° 4, pp.476-488, April 2000.

- [14] E. Sanchez-Sinencio, R.L. geiger, and H. Nevarez-Lozano, "Generation of continuous-time two integrator Loop OTA Filter Structures", IEEE. Trans. Circuits Syst., Vol 35, N° 8, pp.936-946, August 1988.

# Référence

- [1] C. Toumazou, F.J. Lidgey and D.G. Haigh, "Analog IC design: the current mode approach", London, U.K., Peter Peregrinus, 1990.

- [2] **P.R. Gray and R.G. Meyer**, "*Analysis and design of analog integrated circuits*", Third Edition. John Wiley and Sons, singapore, 1993.

- [3] **G. Giustolisi, G. Plamisano, G. Palumbo**, "*CMRR frequency response of CMOS operational transconductance amplfiers*", IEEE. Trans. Instrumentation and Measurements, Vol. 49,N°1,pp.137-143, February 2000.

- [4] **J. C. Voghell**, "Réalisation de filtres analogique Gm-C configurables dans les circuits intégrés", mémoire de maîtrise ès sciences appliquées, école polytechnique, Montréal, 2000.

- [5] **S. Yan and E. Sanchez-Sinencio,** "Low voltage analog Circuit Design techniques: A tutorial, IEICE. Trans. Analog Integrated Circuits and Systems", Vol. E00–A, N° 2, pp 1-17, February 2000,

- [6] T. Itakura, T. Ueno, H. Tanimoto, A. Yasuda, R. Fujimoto, T. Arai, and H. Kokatsu, "A 2.7-V, 200-kHz, 49-dBm, Stopband-IIP3, Low-Noise, Fully Balanced Gm-C Filter IC", IEEE. J. Solid-State Circuits, Vol. 34, N° 8, pp.1115-1199, August 1999.

- [7] **J.E. kardontchik,"**Introduction to the design of transconductore–capacitor filters", 1992, Kluwer Academic Publishers, Boston (USA).

- [8] **J.M. Stevenson, and E. S'anchez-Sinencio,**" *An accurate quality factor tuning scheme for IF and high-Q continuous-Time filters* ", IEEE. J. Solid-State Circuits, Vol.33,N° 12, PP.1970-1978, December, 1998.

- [9] **P.D. Walker, and M.M. Green**, "*An Approach to Fully differential circuit design without common-Mode feedback*", IEEE. Trans. Circuits and Syst. Analog and Digital Signal Processing, Vol 43, N° 11, pp.752-762, November 1996.

- [10] **R. Harjani, R. Heineke, and F. Wang**, "*An Integrated low voltage Class AB CMOS OTA*", IEEE. J. Solid State Circuits, Vol. 34, N° 2,pp 134-141, February 1999.

- [11] **B.Nauta,** "Analoge cmos filters for very high frequencies", 1993, Kluver Acadmic Publishers, Nourvelle MA02061, USA.

- [12] **R. L. Geiger and E. Sánchez-Sinencio,** "Active filter design using operational transconductance amplifiers: A tutorial", IEEE. Circuits and Devices Magazine, Vol. 1, pp.20-32, March 1985.

- [13] W. Tan, A. Karimi-Sanjaani, A. Roithmeier, and A.A. Abidi, "A broad-Band tunable CMOS channel-Select Filter for a low-IF Wireless Receiver Farbod Behbahani", IEEE. J. Solid-State Circuits, Vol.35,N° 4, pp.476-488, April 2000.