الجمهورية الجزائرية الديمقر اطية الشعبية

République Algérienne Démocratique et Populaire

وزارة التعليم العالي والبحث العلمي

Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

Université Mohamed

Khider – Biskra

Faculté des Sciences

Exactes et Sciences de la

Nature et de la Vie

جامعة محمد خيضر - بسكرة كلية العلوم الدقيقة و علوم الطبيعة و الحياة

Thèse présentée en vue de l'obtention du diplôme de:

### **Doctorat LMD**

## **En Physique**

Option :

### Physique des matériaux et composant Photonics

Thème

# a-IGZO تصميم ترنزيستور الشرائح الرقيقة

## Design of a-IGZO Thin film transistors

Par

## Labed Mohamed

Jury

| Nom et Prénom      | Grade           | Etablissement | Qualité      |

|--------------------|-----------------|---------------|--------------|

| Meftah Amjad       | Professeur      | U.M.K. Biskra | Présidente   |

| Sengouga Nouredine | Professeur      | U.M.K. Biskra | Encadreur    |

| Meftah Afak        | Professeur      | U.M.K. Biskra | Examinatrice |

| Oussalah Slimane   | Directeur de la | CDTA. Alger   | Examinateur  |

|                    | recherche       |               |              |

# Acknowledgement

Firstly, I would like to express my sincere gratitude to my advisor **Prof. Sengouga Nouredine** for the continuous support of my Ph.D study and related research, for his patience, motivation, and immense knowledge. His guidance helped me in all the time of research and writing of this thesis. I could not have imagined having a better advisor and mentor for my Ph.D study.

Besides my advisor, I would like to thank the rest of my thesis committee: **Prof. Meftah Amjad**, **Prof. Meftah Afak**, and **Prof. Oussalah Slimane**, for their insightful comments and encouragement, but also for the hard question which incented me to widen my research from various perspectives.

My sincere thanks also goes to Prof. **You Seung Rim** who provided me an opportunity use his data and enhance my simulation results. With his support I make my results more valuable.

I would like to thank the Faculty of Fundamental Sciences (University of Biskra) for its financial support for the scientific visits to the University of Firat and Gazi. I would like to think. Laboratory of Metallic and Semiconducting Materials for all facility.

I would thank all my teachers from first class until today day Especially my first teacher in primary school **Bachir Mohamed**.I thank my fellow labmates in for the stimulating discussions and for all the fun we have had in the last four years. Also, I thank my friend's particular promo master physics 2015. I would thank my friends one by one for all my friend from **bouchagroune** and Turkey and for all people that I meet during in those 4 years.

Last but not the least, I would like to thank my family one by one: My grandparents, my parents to my brother and sister for supporting me spiritually, throughout study in PhD and my life in general.

My thanks again to my family who supported me morally and freed me from my family responsibilities so that I can achieve my goal. Special thanks go to my grandfather and my dad who supported me morally and financially.

اللهم لا علم لنا إلا ما علمتنا ، اللهم علمنا ما ينفعنا وانفعنا بما علمتنا،

إنك أنت العليم الحكيم

## Abstract

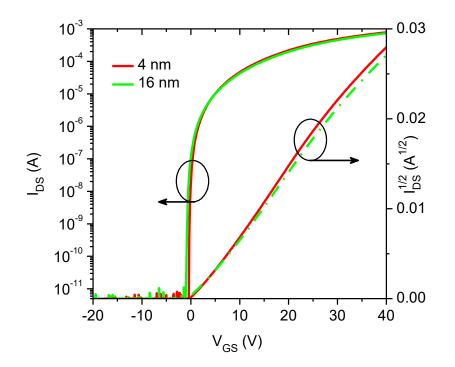

Thin film transistors (TFT) have received great attention due to their applications in flat planed display, e-paper and flexible electronics. a-IGZO based TFTs have shown superior performance as far the stability is concerned. However, some issues remain to be treated properly. In this thesis, numerical simulation (by SILVACO ATLAS) was carried out to investigated three problems. The first, the effect of Hydrogen contamination of a-IGZO was investigated. It was found that donor defects near the valance band has no effect, while the mobility degradation induces a degradation in the TFT performance. Acceptor defects states near valance band is the reason of positive V<sub>th</sub> shift. It is therefore concluded that near valance band defects are not donor defects but acceptor defects with a Gaussian distribution which can also degrade the mobility. The second, is the effect of different gate dielectrics. Four different insulators (SiO<sub>2</sub> Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub> and HfO<sub>2</sub>) are examined. It is found that the output performance is significantly enhanced with high relative permittivity of the insulator. The HfO<sub>2</sub> gate insulator gives the best performance: lower threshold voltage 0.23V and subthreshold 0.09 Vdec<sup>-1</sup>, and higher field effect mobility 13.73 cm<sup>2</sup> s<sup>-1</sup> V<sup>-1</sup>, on current and  $I_{op}/I_{off}$  ratio 2.81 × 10<sup>-6</sup> A,5.06 × 10<sup>12</sup> respectively. Therefore, The HfO<sub>2</sub> gate insulator showed high stability compared with other gate insulators materials. The third is a comparison of simulation to measurement of ultra-thin channel on the TFT performance. The thinner channel layer was found to have a better performance than the thicker channel layer. The 4 nm-thick, ultra-thin a-IGZO TFT exhibited high saturation mobility (7.56 cm<sup>2</sup> V<sup>-1</sup> s<sup>-1</sup>), low threshold voltage (2.73 V), a small value of sub threshold swing (0.22 Vdec<sup>-1</sup>) and a high on/off ratio  $(1.77 \times 10^8)$ . It was also noticed that the threshold voltage (V<sub>th</sub>) shifts negatively as the thickness increases. The 4 nm long channel TFT shows more stability under NIBS and PBS while 16 nm have a strong degradation under NIBS and PBS

## Résumé

Les transistors à couches minces (TFT) ont fait l'objet d'une grande attention en raison de leurs applications en afficheur à écran plat, en papier électronique et en électronique flexible. Les TFT à base d'a-IGZO ont montré des performances supérieures en ce qui concerne la stabilité. Cependant, certains problèmes restent à traiter correctement. Dans cette thèse, une simulation numérique (par SILVACO ATLAS) a été réalisée pour étudier trois problèmes. Le premier est l'effet de la contamination par l'hydrogène d'a-IGZO a été étudié. On a examiné les défauts donneurs près de la bande de valence n'avaient aucun effet, la dégradation de la mobilité induisant une dégradation des performances du TFT. Les états de défauts de type d'accepteur près de la bande de valence sont la raison du décalage positif de tension de seuil. Il est donc conclu que les défauts proches de la bande de valence ne sont pas des défauts donneurs, mais des défauts accepteurs avec une distribution gaussienne qui peuvent également dégrader la mobilité. Le second est l'effet de différents diélectriques de la grille. Quatre isolants différents (SiO<sub>2</sub>, Si<sub>3</sub>N<sub>4</sub>, Al<sub>2</sub>O<sub>3</sub> et HfO<sub>2</sub>) sont examinés. On constate que les performances de sortie sont considérablement améliorées avec une permittivité relative élevée de l'isolant. L'isolant de grille HfO<sub>2</sub> donne les meilleures performances : tension de seuil inférieure 0,23V et 0,09 Vdec<sup>-1</sup> sous-seuil et mobilité de champ supérieure 13,73 cm<sup>2</sup> s<sup>-1</sup> V<sup>-1</sup>, sur le courant et le rapport marche / arrêt 2,81  $\times$  10<sup>-6</sup> A ; 5,06  $\times$  10<sup>12</sup> respectivement. Par conséquent, l'isolant de grille HfO<sub>2</sub> a montré une stabilité élevée par rapport aux autres matériaux isolants de grille. La troisième travaille est une comparaison de la performance entre simulation et mesure de canal ultra mince . La couche de canal la plus mince s'est avérée plus performante que la couche de canal la plus épaisse. Le TFT ultramince a-IGZO de 4 nm d'épaisseur présentait une mobilité de saturation élevée (7,56 cm<sup>2</sup> V<sup>-</sup>  $^{1}$  s<sup>-1</sup>), une tension de seuil faible (2,73 V), une faible valeur de sous-seuil (0,22 Vdec<sup>-1</sup>) et un rapport du curent marche / arrêt élevé  $(1,77 \times 10^8)$ . Il a également été remarqué que la tension de seuil (V<sub>th</sub>) se déplace négativement à mesure que l'épaisseur augmente. Le TFT à canal long de 4 nm montre plus de stabilité sous NIBS et PBS alors que 16 nm ont une forte dégradation sous NIBS et PBS

ملخص

ترانزستور الشرائح الرقيقة حضى باهمتام كبير من اجل تطبيقاته في الشاشات المصطحة ، الاوراق الالكترونية و الالكترونيات المرنة الترنستور انديوم غاليوم زينك اكسيد لا بلوري (a-IGZO) اظهر خصائص مميزة و اسقرار جيد بالاضافة الى نتائج الجيدة لكن هناك بعض الظو اهر التي يجب ان تدرس بإهتمام. في هذا العمل استعملت المحاكات الرقمية بواسطة (SILVACO ATLAS) من اجل در اسة ثلاث اشكاليات. او لا، در اسة تأثير شوائب الهيدروجين في مادة انديوم غاليوم زينك اكسيد. الدر اسة وجدت ان العيوب المانحة بالقرب من عصابة التكافئ ، ليس لها تأثير ، تقهقر الحركية يتسبب في تراجع أداء ترانزستور الشرائح الرقيقة. العيوب الاخدة بالقرب من عصابة التكافئ هي سبب الانزياح الى الموجب لقيم جهد العتبة. وجد ان العيوب من القرب عصابة التكافئ هي عيوب اخذة و ليست مانحة بالاضافة الى انها ذات توزيع غوسي كما ان هذه العيوب تسبب في تراجع قيم الحركية. ثانيا، تأثير عدة انواع من عوازل كعازل لبوابه، تم استعمال اربعة عوازل ( اكسد السليوم ، نيتريد السليسوم ، اكسيد الاليمنيوم ، و اكسيد الهفنيوم) لدراسة تأثير العازل ، وجد ان اداء ترانزستور يتحسن بشكل ملحوظ مع عوازل ذات ثابت عزل كبير. العازل اكسيد الهفنيوم اظهر افضل نتائج حيث قيمة جهد العتبة 0.23 V و انحراف ما فوق جهد العتبة 0.09 Vdec<sup>-1</sup> . حركية التأثير الحقلي 13.73 cm<sup>2</sup> s<sup>-1</sup> V الاشتغال و نسبة تيار الاشتغال على تيار الاطفاء كانت على توالى 6-10 × A 2.81 × 10<sup>12</sup> بالاضافة اكيسد الهفنيوم اظهر استقرار جديد مقارنة مع العوازل الاخرى في هذه الدراسة. ثالثًا تمت مقارنة بين محاكات و قياسات تجربية لترانزستور ذو قناة جد رقيقة القناة ذو الطبقة الرقيقة اظهرت اداء افضل من القناة الاخثن . السمك 4 نانو متر للقناة ترنسيتور انديوم غاليوم زينك اكسيد لا بلوري اظهرت حركية تشبع عالية (7.56 cm² V<sup>-1</sup> s<sup>-1</sup>) جهد عتبة صغير (2.73 V) ، و قيم صغيرة للانحارف ما فوق جهد العتبة (0.22 Vdec<sup>-1</sup>) و قيم علية لنسبة التيار الشغيل على تيار الأطفاء .(108 × 1.77) . كما تم ملاحظة أن مع زيادة في السمك نلاحظ انزياح جهد العبتة نحو الاتجاه السالب . السمك 4 نانو متر للقناة ترنستور اظهر اكثر استقرار تحت اجهاد الجهد السالب و الاضاءة و اجهاد الجهد الموجب بينما 16 نانو متر اظهر اكثر تقهقر تحت اجهاد الجهد السالب و الاضاءة و اجهاد الجهد الموجب.

# **Table of Contents**

| Abstract       | I                                            |

|----------------|----------------------------------------------|

| Résumé         |                                              |

| ملخص           | III                                          |

| Table of Cor   | ntentsIV                                     |

| List of Figure | esVIII                                       |

| List of Table  | s XII                                        |

| General intro  | oduction                                     |

| Reference      | s4                                           |

| Chapter I Hi   | story and physics of thin film transistors   |

| I.1 Introdu    | action                                       |

| I.2 History    | y of thin film transistors                   |

| I.2.1          | Field effect device                          |

| I.2.2          | TFT based on $a - Si: H$ and poly crystal Si |

| I.2.3          | Organic TFT 12                               |

| I.2.4          | Transparent Oxide Semiconductors TFT         |

| I.3 Physic     | s and modeling TFTs 16                       |

| I.3.1          | Ideal MIS Capacitor structure                |

| I.3.2          | Gate bias and threshold voltage              |

| I.3.3          | MOSFET operation                             |

| I.3.4          | Current-Voltage modulation                   |

| I.4 Thin f            | Im Transistor                                              |    |

|-----------------------|------------------------------------------------------------|----|

| I.5 Refere            | nces                                                       |    |

| Chapter II a          | -IGZO thin films transistors                               | 34 |

| II.1 Introd           | luction                                                    |    |

| II.2 IGZC             | properties                                                 |    |

| II.2.1                | Atomic structure                                           |    |

| II.2.2                | Electronic structure of oxide                              |    |

| II.2.3                | Band structure                                             |    |

| II.2.4                | Origin large Electron mobility in AOS                      |    |

| II.2.5                | Optical properties of a-IGZO                               | 41 |

| II.2.6                | Defect levels in IGZO                                      | 43 |

| II.3 Grow             | th a-IGZO thin films by sol-Gel                            | 46 |

| II.3.1                | Spin coating                                               |    |

| II.4 Chara            | cterization a-IGZO thin films                              |    |

| II.4.1                | X-Ray Diffraction characterization                         |    |

| II.4.2                | UV-VIS Spectroscopy                                        |    |

| II.5 Fabrie           | cation a-IGZO TFT                                          | 54 |

| II.5.1                | TFT structure                                              | 54 |

| II.5.2                | TFT process fabrication                                    | 57 |

| II.6 <sup>–</sup> TFT | characteristics and performance indexes                    | 59 |

| II.6.1                | I-V characteristics                                        | 59 |

| II.7 Refer            | ences                                                      | 63 |

| Chapter III S         | Simulation and fabrication of a-IGZO thin film transistors | 66 |

| III.1 Intro           | duction                                                    |    |

| III.2 Simu   | lation IGZO thin film transistors                                             |

|--------------|-------------------------------------------------------------------------------|

| III.2.1      | Fundamentals of Device Simulation67                                           |

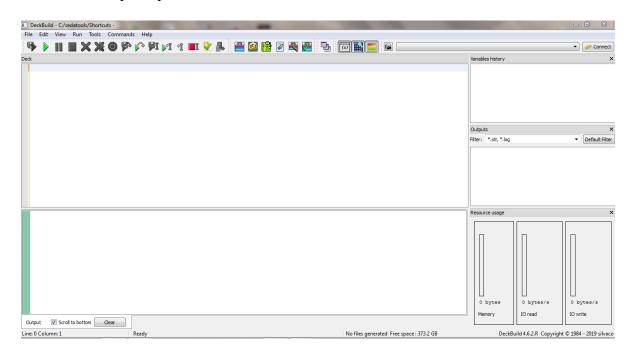

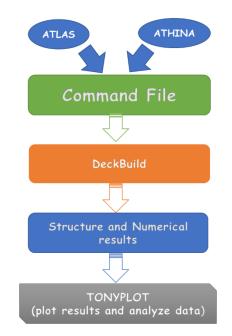

| III.2.2      | Simulation by SILVCO TCAD                                                     |

| III.2.3      | Commands File71                                                               |

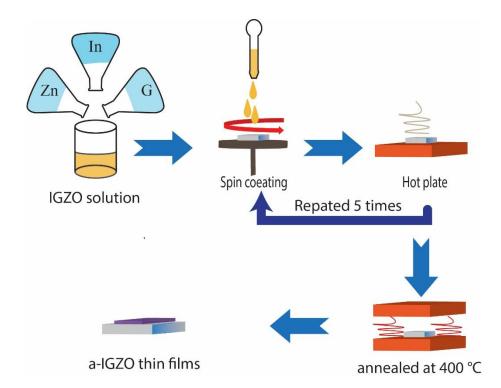

| III.3 Fabri  | ication of thin film transistors by solution process                          |

| III.3.1      | Cleaning79                                                                    |

| III.3.2      | Deposition a-IGZO thin films                                                  |

| III.3.3      | Electrode deposition                                                          |

| III.4 Refe   | rences                                                                        |

| Chapter IV I | Results and discussion                                                        |

| IV.1 Intro   | duction                                                                       |

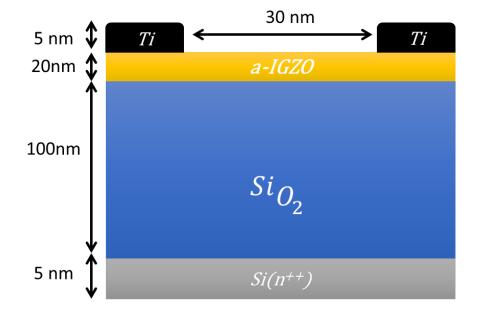

| IV.2 TFT     | Structure and physical model                                                  |

| IV.3 Effec   | ct of deep defects on the performance of amorphous indium gallium zinc oxide  |

| thin film t  | ransistor                                                                     |

| IV.3.1       | Near valance band defects                                                     |

| IV.3.2       | Effect of the electron mobility96                                             |

| IV.4 Simu    | lation the influence of the gate dielectrics in amorphous indium-gallium-zinc |

| oxide thin   | film transistors reliability                                                  |

| IV.4.1       | TFT Structure                                                                 |

| IV.4.2       | The effect of insulator on operation a-IGZO TFTs99                            |

| IV.4.3       | Impact of insulators on TFTs <i>Vth</i> degradation105                        |

| IV.4.4       | Effect of fixed charge in HfO <sub>2</sub> insulator:                         |

| IV.4.5       | Effect of HfO <sub>2</sub> thickness:                                         |

| IV.5 Num     | erical simulation on thickness dependency and bias stress test of ultrathin   |

| IGZO thir    | n-film transistors by a solution process                                      |

| IV.6 Depo    | osition a-IGZO thin films by sol gel method124                                |

| IV.7 References                        |  |

|----------------------------------------|--|

| Conclusion                             |  |

| Appendix: Publications and Conferences |  |

# **List of Figures**

| Figure I-1 Diagram of the first field-effect electronic device9                                                     |

|---------------------------------------------------------------------------------------------------------------------|

| Figure I-2 Diagram of an early field-effect device9                                                                 |

| Figure I-3 TFT structure of Weimer's top-gate staggered CdS TFT structure 10                                        |

| Figure I.I-4 First TFT with a-Si like active layer 11                                                               |

| Figure I-5 the first Organic thin films transistor 12                                                               |

| Figure I-6. The first TFT based on SnO <sub>2</sub> 14                                                              |

| Figure I-7. The first a-IGZO deposited at room temperature by Nomura et al. a) $IDS -$                              |

| VDS curve b) structure of a-IGZO TFT c) the flexible substrate 15                                                   |

| Figure I-8 Metal Insulator Semiconductor system 16                                                                  |

| Figure I-9 Energy-band diagrams of ideal MIS capacitors at equilibrium $(V = 0)$ 17                                 |

| Figure I-10 Energy-band diagrams for ideal MIS capacitors under different bias                                      |

| conditions: (a) accumulation, (b) depletion, and (c) inversion. The semiconductor substrate                         |

| <i>is n-type</i> 18                                                                                                 |

| Figure I-11. 2 D illustration cross section of a MOSFET 23                                                          |

| Figure I-12: Cross-section of MOSFET, in the on-state, for different values of drain bias                           |

| $V_D$ : a) $V_D = 0$ , b) $V_D < V_G - V_T$ , c) at pinch-off, with $V_D = V_G - V_T = V_{D(sat)}$ , and d) $V_D$ > |

| $V_{D(sat)}$ showing channel shortening 25                                                                          |

| Figure I.I-13. Measured MOSFET output characteristics showing the linear and saturation                             |

| operating regimes 26                                                                                                |

| Figure I-14 Schematics showing show the difference between MOSFET and TFT 28                                        |

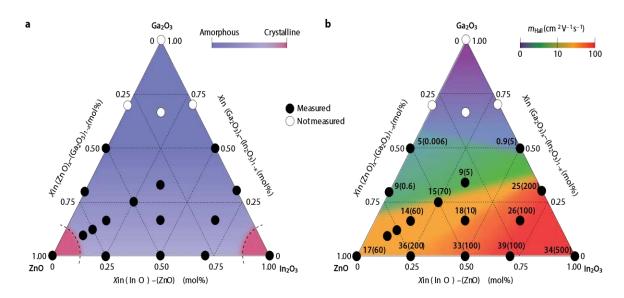

| Figure II-1 (a) Amorphous formation and (b) electron transport properties $In_2O_3$ , $Ga_2O_3$                     |

| thin films. The values in (b) denote the electron Hall mobility $(cm^2V^{-1} s^{-1})$ with density $(10^{18}$       |

| $cm^{-3}$ ) in parentheses 35                                                                                       |

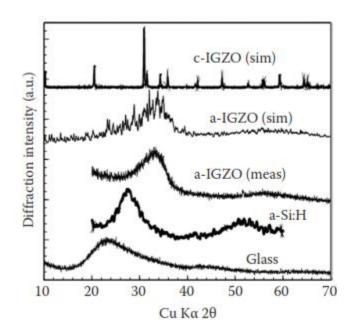

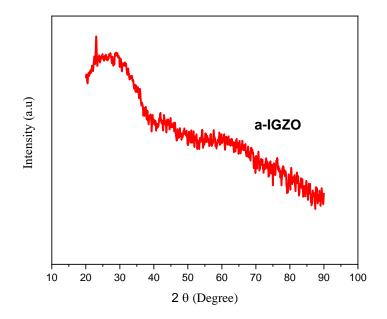

| Figure II-2 XRD result 36                                                                                           |

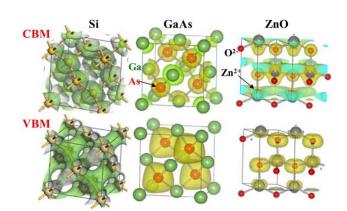

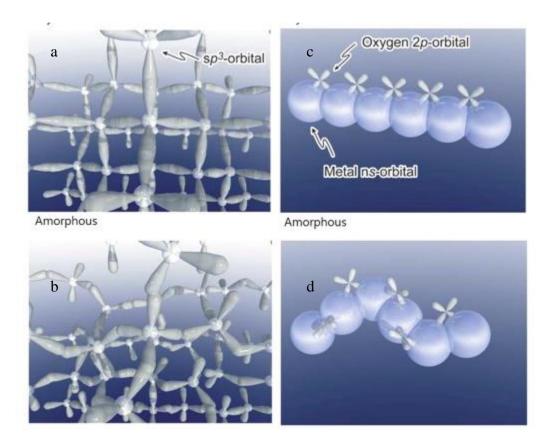

| Figure II-3 Wave functions of representative semiconductors such as Si, GaAs and ZnO. 37                            |

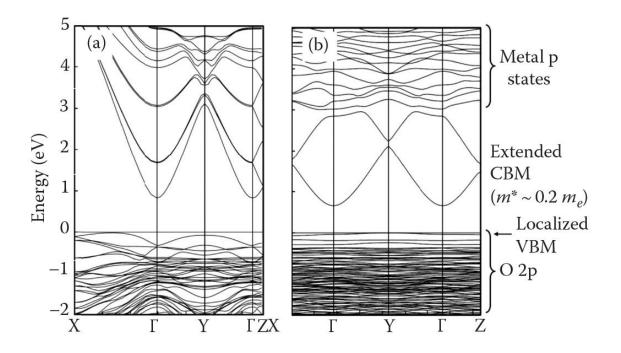

| Figure II-4 Schematic electronic structures of silicon and ionic oxide semiconductors (a-c)                         |

| Bandgap formation mechanisms in (a) covalent and (b,c) ionic semiconductors 37                                      |

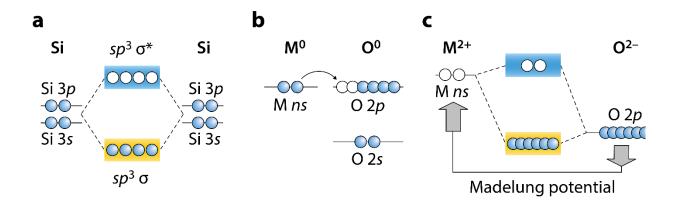

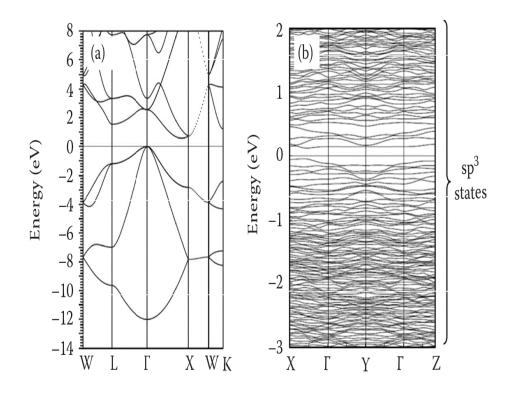

| Figure II-5 (Pseudo-)band structures of (a) c-InGaZnO 4 and (b) a-InGaZnO <sub>4</sub> 38                           |

| Figure II-6 (Pseudo-)band structures of (a) c-Si and (b) a-Si 39                                                    |

| Figure II-7 Schematic orbital drawings of carrier pathways in (a) crystalline Si, (b)   |      |

|-----------------------------------------------------------------------------------------|------|

| amorphous Si, (c) crystalline oxides, and (d) amorphous oxides                          | 41   |

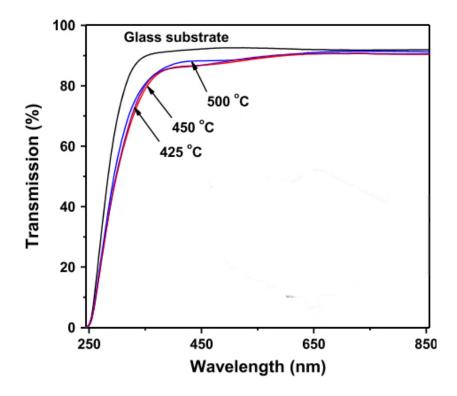

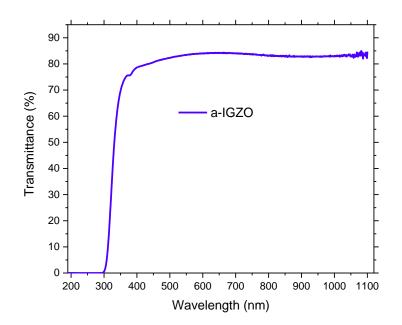

| Figure II-8 Optical transmittance spectra of glass substrate and glass/a-IGZO thin file | п    |

| samples                                                                                 | 42   |

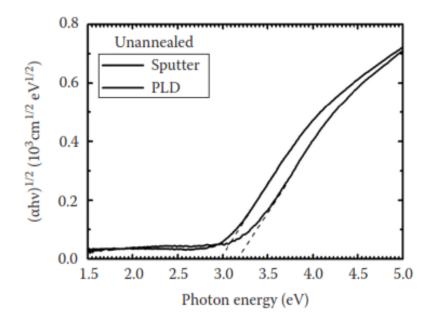

| Figure II-9 Optical. absorption. spectra. of. a-IGZO. films. deposited. by. RF. magnet  | ron. |

| sputtering. and. PLD at RT plotted. in. terms of Tauc's plot                            | 43   |

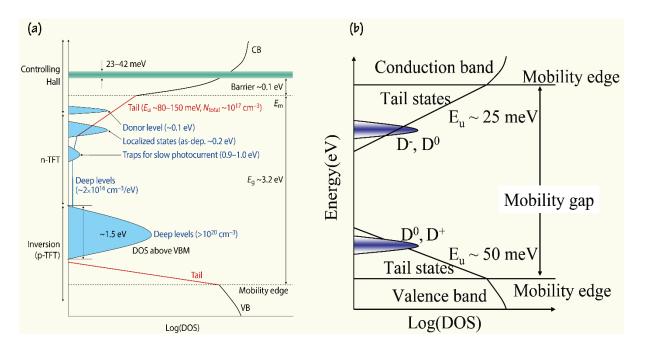

| Figure II-10 Schematic models of subgap DOS in (a)a-IGZO and (b) a-Si:H.                | 44   |

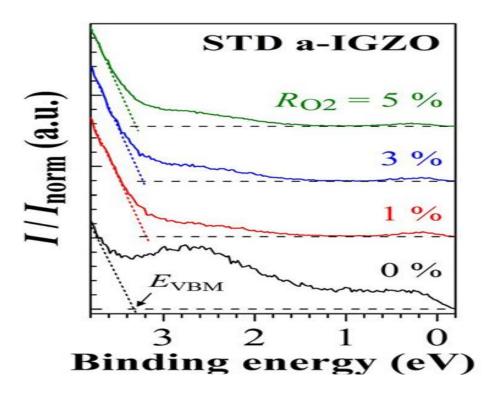

| Figure II-11 HAXPES spectra around the band gap region                                  | 46   |

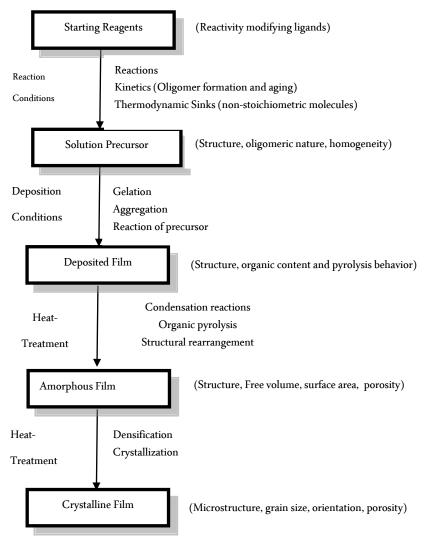

| Figure II-12 Processing stages in chemical solution deposition of thin films. Controlla | ble  |

| parameters are shown on the left                                                        | 48   |

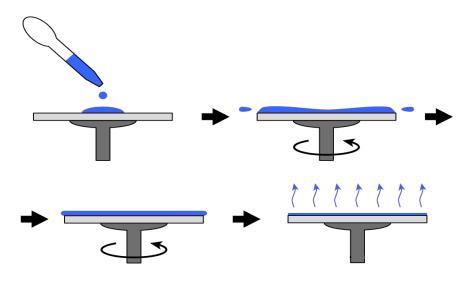

| Figure II-13 Spin coating method                                                        | 49   |

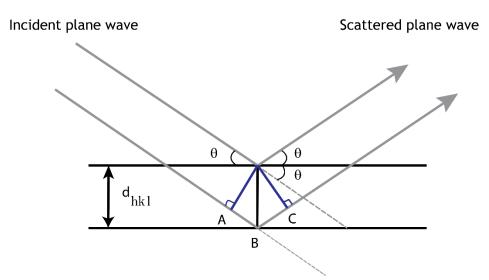

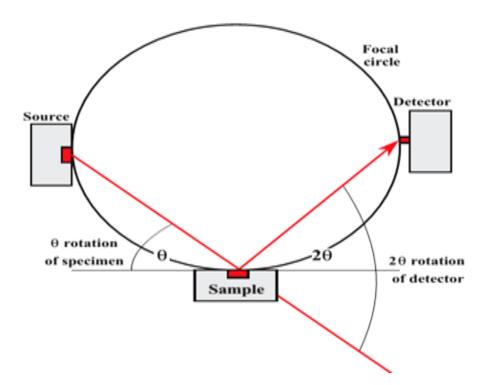

| Figure II-14 Geometric illustration of Bragg diffraction. For constructive              |      |

| interference, $n\lambda = AB + BC = 2dsin\theta$ .                                      | 51   |

| Figure II-15 A sample mounted on a goniometry which can be rotated about one or m       | ore  |

| axis, and a detector which travels along the focusing circle in the Bragg–Brentano      |      |

| geometry                                                                                | 52   |

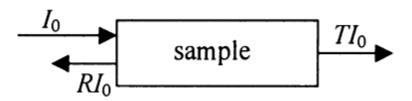

| Figure II-16 Light transmission and reflection from a sample                            | 52   |

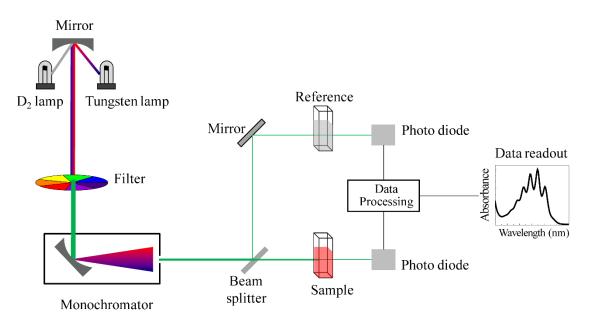

| Figure II-17 Schematic of UV- visible spectrophotometer                                 | 53   |

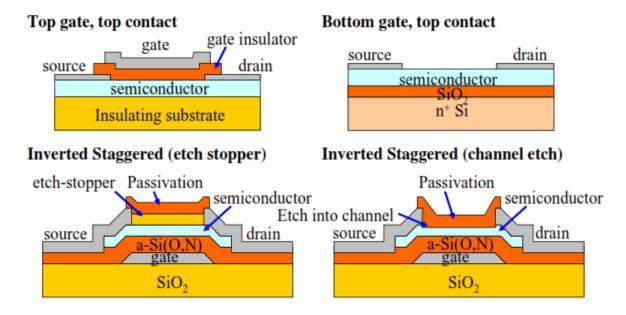

| Figure II-18 of the four different TFT structures                                       | 55   |

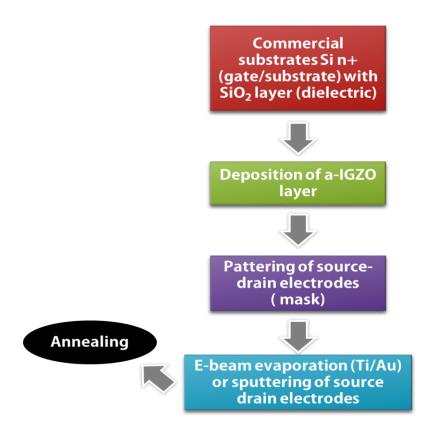

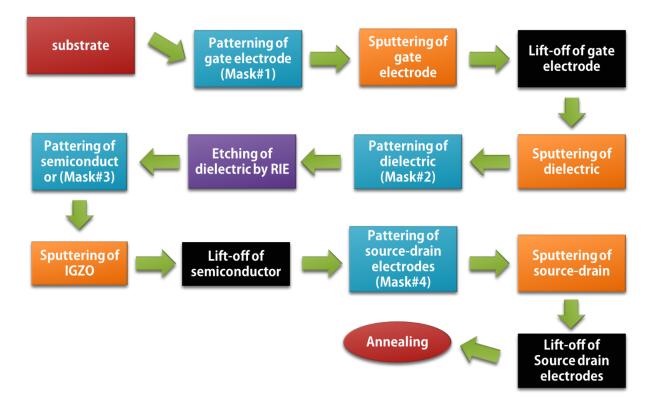

| Figure II-19 Process flow used to produce oxide TFTs bottom gate using commercial       |      |

| <i>Si/SiO</i> <sub>2</sub>                                                              | 57   |

| Figure II-20 Process flow used to produce oxide TFTs Inverted staggered gate using      |      |

| employing glass substrates                                                              | 58   |

| Figure II-21 Typical a) output and b) transfer characteristics of a n-type oxide TFT    | 59   |

| Figure III-1 DECKBUILD window                                                           | 70   |

| Figure III-2 Process of simulation by SILVACO                                           | 71   |

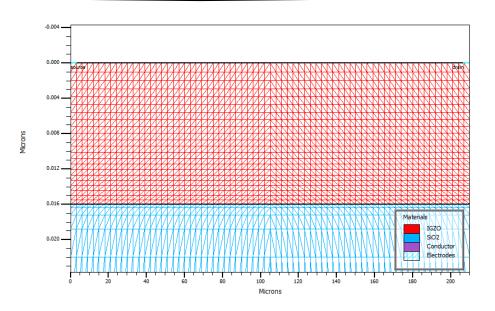

| Figure III-3 2D mesh a-IGZO TFT                                                         |      |

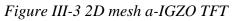

| Figure III-4 2D structure of a-IGZO TFT                                                 | 74   |

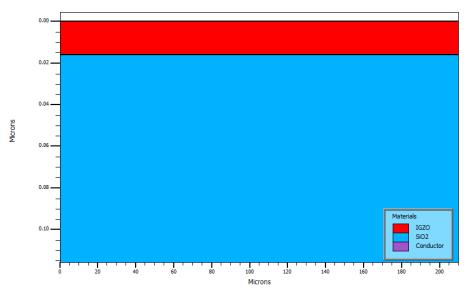

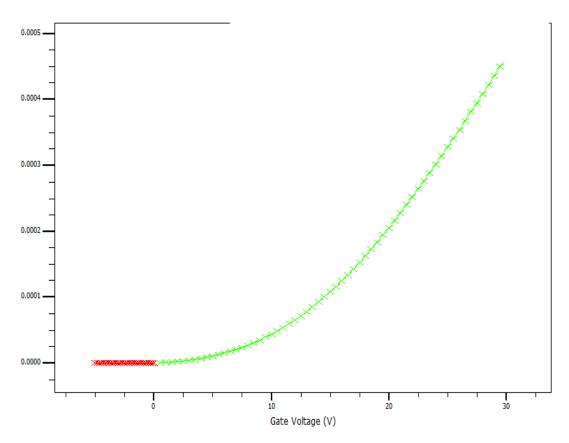

| Figure III-5 I <sub>DS</sub> -V <sub>GS</sub> characteristics                           | 78   |

| Figure III-6 Deposition a-IGZO thin films by Spin coating                               | 80   |

| Figure III-7 The illustration showing how shadow mask is used                           | 81   |

| Figure IV-1: A two-dimension schematic view of the TFT structure 84                                         |

|-------------------------------------------------------------------------------------------------------------|

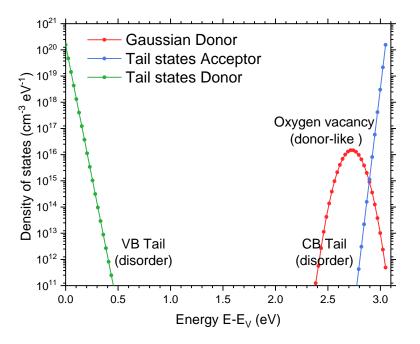

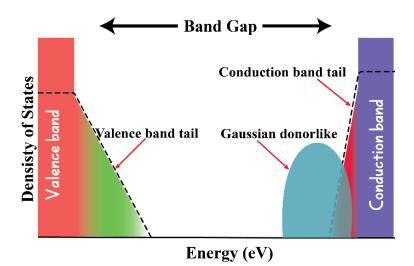

| Figure IV-2: Density of states in a-IGZO 88                                                                 |

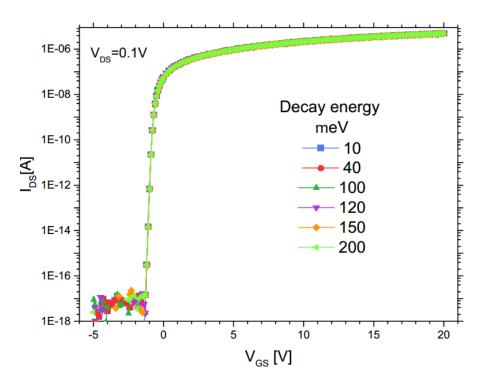

| Figure IV-3: The transfer characteristics for different decay energies91                                    |

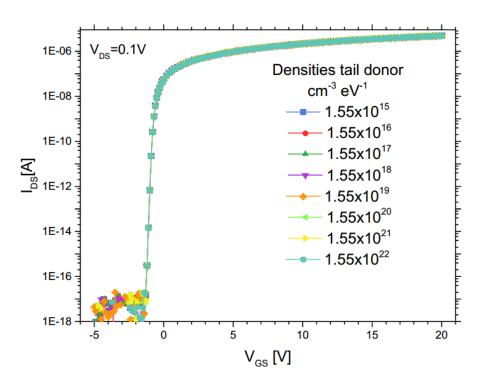

| Figure IV-4: The effect of the donor tail densities on the TFT transfer characteristics 92                  |

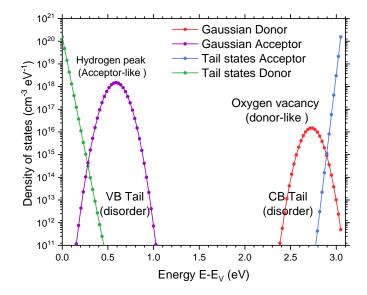

| Figure IV-5: Density of states in a-IGZO with Gaussian acceptor states93                                    |

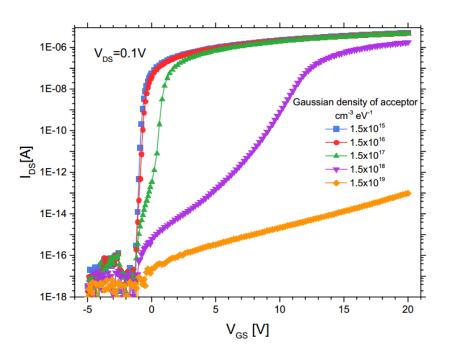

| Figure IV-6: The effect of Gaussian acceptor density on the TFT transfer characteristics. 94                |

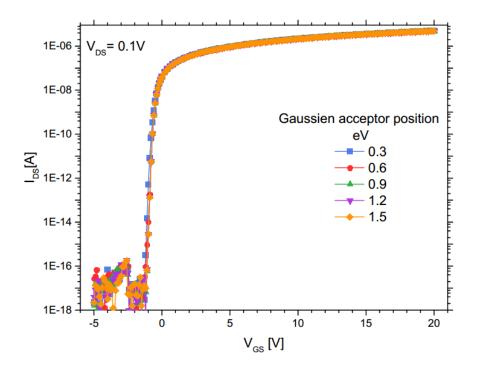

| Figure IV-7: The effect of the energetic position of the Gaussian acceptor on the TFT                       |

| transfer characteristics 95                                                                                 |

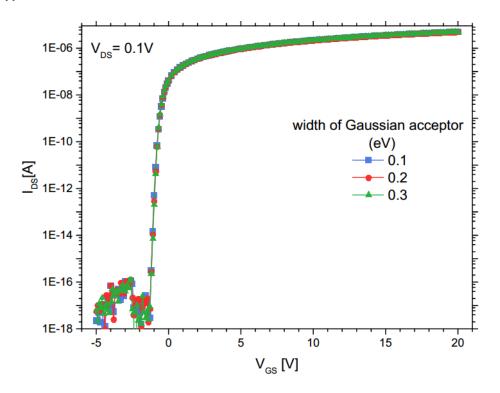

| Figure IV-8: The effect of Gaussian acceptor width on the TFT transfer characteristics 96                   |

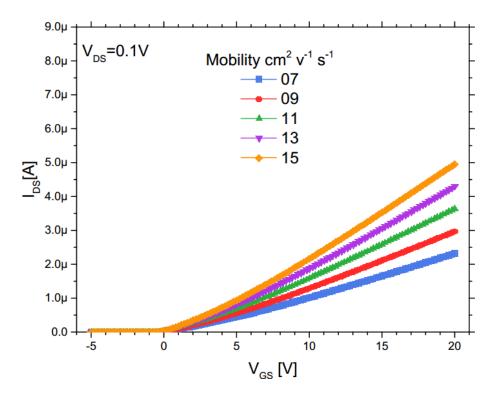

| Figure IV-9: The effect of the degradation of the mobility on the transfer characteristics of               |

| <i>the TFT97</i>                                                                                            |

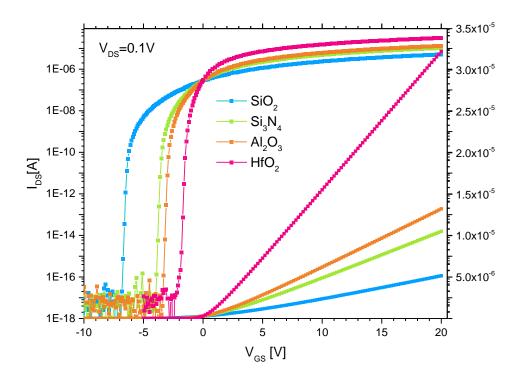

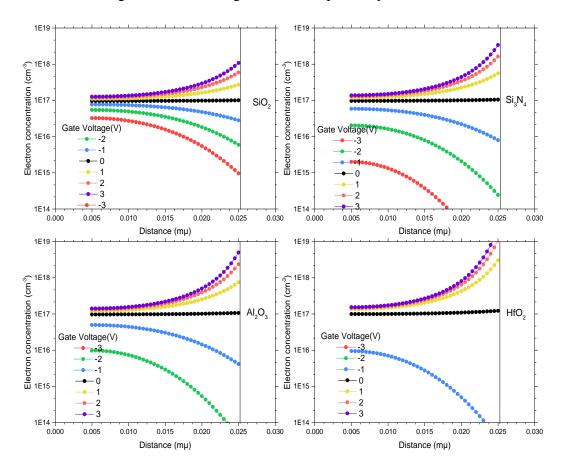

| Figure IV-10: The transfer characteristics for different insulators layers 100                              |

| Figure IV-11: The electron concentration, for different gate voltages and $V_{DS}=0.1$ V, for the           |

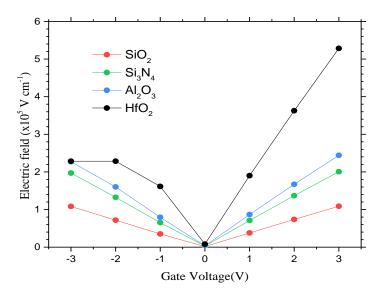

| insulators 102                                                                                              |

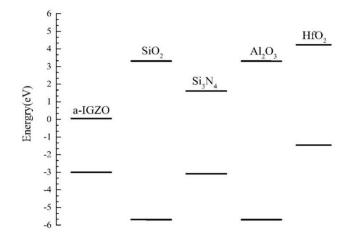

| Figure IV-12: The Electric field for different gate insulators103                                           |

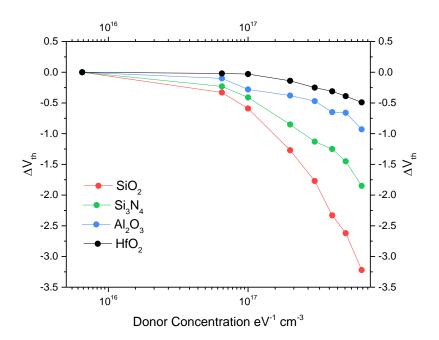

| Figure IV-13:Band offsets for dielectrics on a-IGZO105                                                      |

| Figure IV-14: The threshold shift $\Delta V_{th}$ versus the Gaussian donor density per unit energy         |

| for different insulator layers106                                                                           |

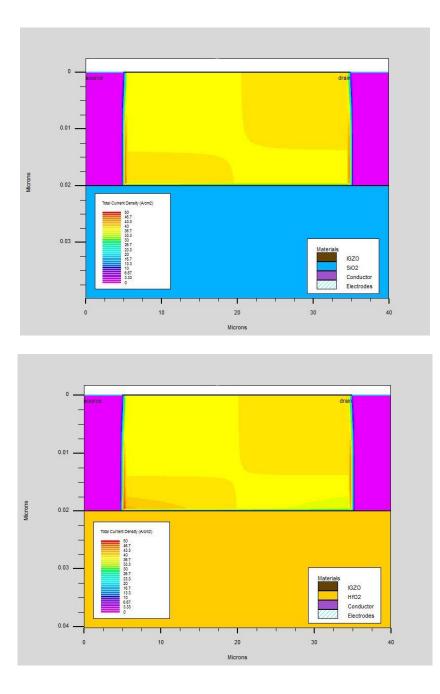

| Figure IV-15: The total current density for (a) $SiO_2$ insulator layers and (b) $HfO_2$ insulator          |

| <i>layers 108</i>                                                                                           |

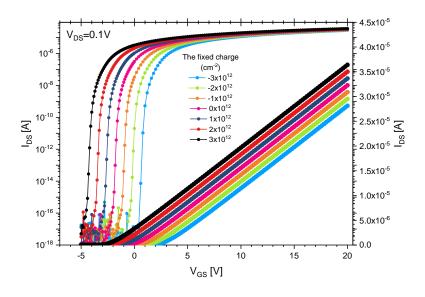

| Figure IV-16:Transfer characteristics of the TFT with the fixed charge states in the                        |

| insulator dielectric (HfO <sub>2</sub> )110                                                                 |

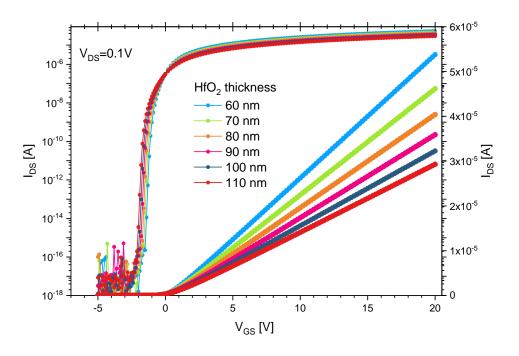

| Figure IV-17: The transfer characteristics for different thickness of HfO2111                               |

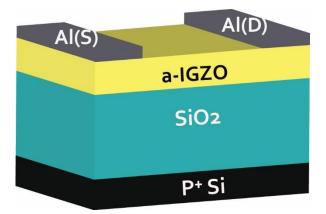

| Figure IV-18. A schematic view of the a-IGZO TFT structure used in the simulation112                        |

| Figure IV-19. DOS distribution for a-IGZO113                                                                |

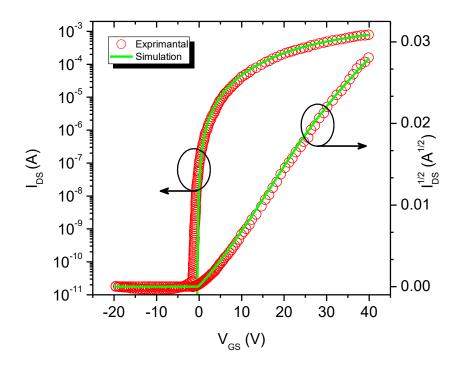

| Figure IV-20. Experimental and simulated transfer characteristic curves for a-IGZO TFT.                     |

| 116<br>Figure IV-21. The simulated transfer characteristics for different thicknesses of the TFT<br>channel |

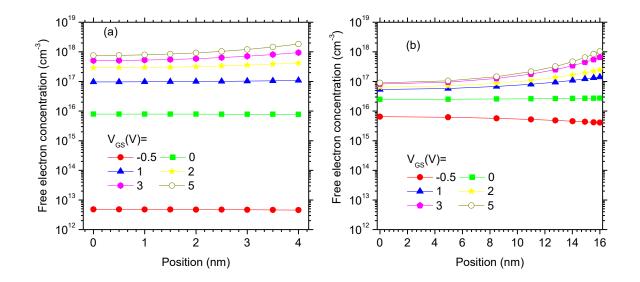

| Figure IV-22. The extracted free electron density from simulation for 4 nm (a) and (b) for                  |

| 16 nm channel thickness in TFTs for different gate voltages119                                              |

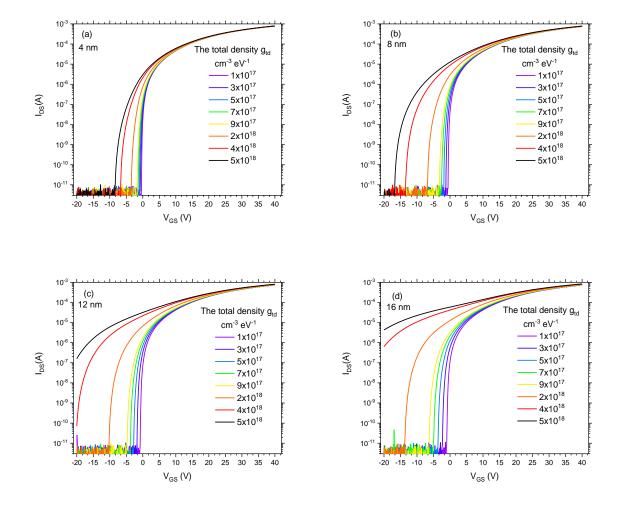

| Figure IV-23. The effect of NBIS (creation of Gaussian donor states) on the transfer        |

|---------------------------------------------------------------------------------------------|

| characteristics for: a) 4 nm a-IGZO TFT b) 8 nm a-IGZO TFT a) 12 nm a-IGZO TFT d) 16        |

| nm a-IGZO TFT120                                                                            |

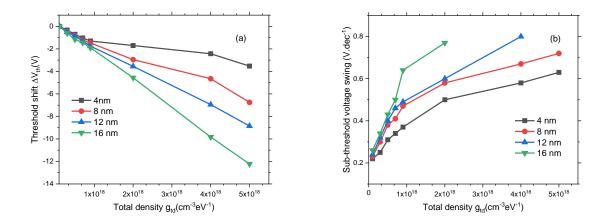

| Figure IV-24. Effect of NBIS (creation of Gaussian donor states) for different thickness on |

| extracted output parameters: a) Threshold shift b) Sub-threshold voltage swing121           |

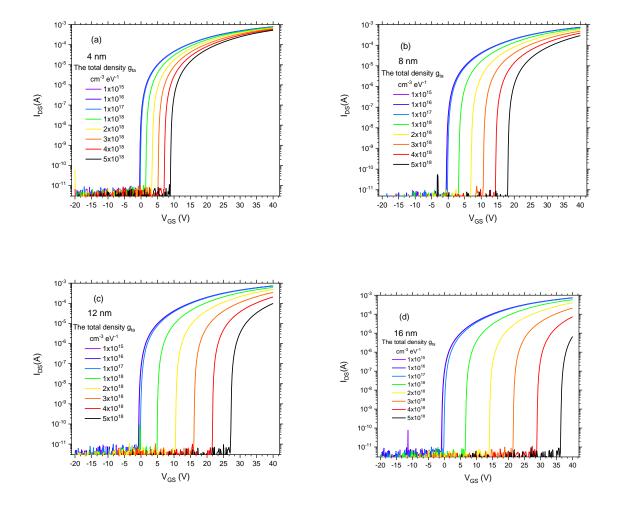

| Figure IV-25. The simulated transfer characteristics after PBS for: for: a) 4 nm a-IGZO     |

| TFT b) 8 nm a-IGZO TFT a) 12 nm a-IGZO TFT d) 16 nm a-IGZO TFT 122                          |

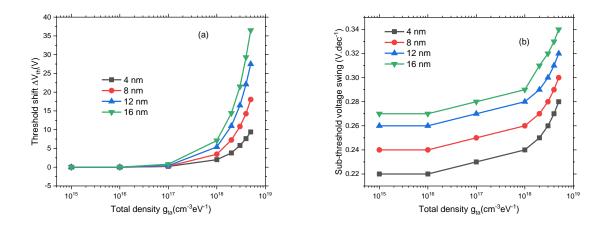

| Figure IV-26. Effect of PBS (creation of Gaussian acceptor states) for different thickness  |

| on extracted output parameters: a) Threshold shift b) Sub-threshold voltage swing 123       |

| Figure IV-27 Transmittance spectra of a-IGZO film124                                        |

| Figure IV-28 XRD patterns of a-IGZO thin films125                                           |

# **List of Tables**

| Table I-1: Polarity relationship between band bending, surface field and space charge in      |

|-----------------------------------------------------------------------------------------------|

| an MIS                                                                                        |

| TableII-1: Summary of film deposition sol-gel spin coating.       49                          |

| Table III-1The order of Atlas commands    72                                                  |

| Table IV-1: The physical parameters of the different layers of the a-IGZO TFT used in this    |

| work                                                                                          |

| Table IV-2: The effect of the density of the Gaussian acceptor on the output parameters of    |

| <i>the TFT.</i>                                                                               |

| Table IV-3: The effect of mobility on the output parameters of the TFT.       97              |

| Table IV-4: The physical parameters of the different layers insulators layers for a-IGZO      |

| <i>TFT</i>                                                                                    |

| Table IV-5: The effect of different insulators layer on the output parameters of the TFT. 101 |

| Table IV-6: The physical parameters of the different layers of the a-IGZO TFT used in this    |

| section                                                                                       |

| Table IV-7: Comparison of extracted a-IGZO TFT parameters between experimental and            |

| simulation                                                                                    |

## **General introduction**

Transistors take much attention in research due to its their application in logical circuits. The development in transistors technology leads to discovery of metal oxide semiconductors transistor which was the secrete of developing numerical technology. Thin film transistors (TFT) is one type of Metal Oxide Semiconductor (MOS) transistors and which have received much attention due to their ease fabrication and wide range applications especially in flat panel display and mobile display.

Many semiconductor materials were used as channel in TFT. a-Si:H was most material used in TFT. Hydrogenated amorphous silicon (a-Si:H) have many disadvantages such as low mobility [1], high defects [2], and instability [3] and it has complicated fabrication [2]. Zinc oxide (ZnO), indium oxide (In<sub>2</sub>O<sub>3</sub>) and tin oxide (SnO<sub>2</sub>), known as transparent oxide semiconductors (TOS) are widely used in TFTs due to their unique properties such high stability in atmosphere, ease of fabrication and high mobility compared to a-Si:H. Most TOS require high temperature to fabricate plus the problems of grain boundary [4]. Those two problems are very critical for industry application. Amorphous transparent oxide (AOS) tend to replace binary TOS and Si:H in TFT technology. AOS can be fabricated at room temperature and deposited on very large scale which attracted TFT producers [5]. Amorphous Indium gallium zinc oxide (a-IGZO) is the most famous AOS. a-IGZO has attracted great attention because of its good properties (high mobility, high transmittance, low defects, atmosphere stability) and good performance a-IGZO based TFTs (small threshold voltage and subthreshold and high mobility, on current) [6]. Designing an optimal a-IGZO TFT is still a challenge, however.

The stability of a-IGZO TFTs, defined by the threshold voltage shift, is a crucial issue for its practical applications. There is an intense ongoing research work investigating possible causes of the threshold voltage shift ( $\Delta V_{th}$ ). One of such possible causes is oxygen vacancies near the conduction band minimum (CBM) states [7]–[9]. The oxygen vacancies are the reason of negative V<sub>th</sub> shift. The presence of hydrogen creates defect states near the valance band maximum (VBM) [10], [11]. The oxygen disorder is origin of deep defects states [12]. The high density subgap defects in a very deep energy region just above the valance band maximum (near-VBM states) may be other causes of the instability. However, it is not yet known what kind of influence defect near VBM states have on the device performance such as threshold voltage shift. As an important part of the TFT, the gate insulator plays a vital role in its performance. Various gate insulators, such as, silicon dioxide (SiO<sub>2</sub>) [13], silicon nitride (Si<sub>3</sub>N<sub>4</sub>) [14], [15], Aluminum oxide (Al<sub>2</sub>O<sub>3</sub>) [16], [17], and hafnium oxide (HfO<sub>2</sub>) [18], [19] have been investigated for use in TFTs.

The thickness of channel is an important factor to optimize work of a-IGZO TFT. It has been observed that the a-IGZO TFT stability improved with increasing channel thickness [20]–[22]. By contrast other work showed that a decrease in the TFT channel thickness enhanced its stability [23]–[25]. Therefore, it seems that the experimental investigation the effect of thickness on the stability is not conclusive due to many factors. For example, contamination during the TFT fabrication, density of defects in the channel films, morphology of these films or absorption of ambient gases during or after fabrication. In this work and using numerical simulation, the effect of gate insulators, the channel thickness effect and the defects created by Hydrogen on a-IGZO TFTs performance and stability.

2

This thesis contains four chapters. In the first chapter the history and physics of thin film transistors is presented. Second chapter deals with the operation and performance of a-IGZO thin films transistors. The simulation and fabrication of a-IGZO TFT are presented in the third chapter. Finally, the fourth chapter details the results obtained in this thesis and their discussion. This thesis finishes with a conclusion and recommendation for further work.

#### References

- [1] a M. Meftah, a F. Meftah, F. Hiouani, and a Merazga, "Numerical simulation of the defect density influence on the steady state response of a silicon-based p-i-n cell," *J. Phys. Condens. Matter*, vol. 16, no. 12, pp. 2003–2016, 2004.

- [2] S. C. Deane, F. J. Clough, W. I. Milne, and M. J. Powell, "The role of the gate insulator in the defect pool model for hydrogenated amorphous silicon thin film transistor characteristics," *J. Appl. Phys.*, vol. 73, no. 6, pp. 2895–2901, 1993.

- [3] R. B. Wehrspohn *et al.*, "Relative importance of the Si–Si bond and Si–H bond for the stability of amorphous silicon thin film transistors," *J. Appl. Phys.*, vol. 87, no. 1, pp. 144–154, 2000.

- [4] K. Nomura, A. Takagi, T. Kamiya, H. Ohta, M. Hirano, and H. Hosono,

"Amorphous oxide semiconductors for high-performance flexible thin-film transistors," *Japanese J. Appl. Physics, Part 1 Regul. Pap. Short Notes Rev. Pap.*, vol. 45, no. 5 B, pp. 4303–4308, 2006.

- [5] H. Hosono, "Ionic amorphous oxide semiconductors: Material design, carrier transport, and device application," *J. Non. Cryst. Solids*, vol. 352, no. 9-20 SPEC. ISS., pp. 851–858, 2006.

- [6] J. Yeon Kwon and J. Kyeong Jeong, "Recent progress in high performance and reliable n-type transition metal oxide-based thin film transistors," *Semicond. Sci. Technol.*, vol. 30, no. 2, p. 24002, 2015.

- [7] K. Nomura *et al.*, "Subgap states in transparent amorphous oxide semiconductor, In -Ga - Zn - O, observed by bulk sensitive x-ray photoelectron spectroscopy Subgap

states in transparent amorphous oxide semiconductor , In - Ga - Zn - O , observed by bulk sensitive x-ray ph," vol. 202117, no. 2008, 2012.

- [8] K. Nomura, T. Kamiya, E. Ikenaga, H. Yanagi, K. Kobayashi, and H. Hosono,

"Depth analysis of subgap electronic states in amorphous oxide semiconductor, a-In-Ga-Zn-O, studied by hard x-ray photoelectron spectroscopy," in *Journal of Applied Physics*, 2011, vol. 109, no. 7.

- [9] W. T. Chen *et al.*, "Oxygen-dependent instability and annealing/passivation effects in amorphous In-Ga-Zn-O thin-film transistors," *IEEE Electron Device Lett.*, vol. 32, no. 11, pp. 1552–1554, 2011.

- [10] A. Hino, S. Morita, S. Yasuno, T. Kishi, K. Hayashi, and T. Kugimiya, "Effect of H and OH desorption and diffusion on electronic structure in amorphous In-Ga-Zn-O metal-oxide-semiconductor diodes with various gate insulators," *J. Appl. Phys.*, vol. 112, no. 11, 2012.

- K. Nomura, T. Kamiya, and H. Hosono, "Effects of Diffusion of Hydrogen and Oxygen on Electrical Properties of Amorphous Oxide Semiconductor, In-Ga-Zn-O," *ECS J. Solid State Sci. Technol.*, vol. 2, no. 1, pp. P5–P8, 2013.

- [12] S. Sallis *et al.*, "Origin of deep subgap states in amorphous indium gallium zinc oxide: Chemically disordered coordination of oxygen," *Appl. Phys. Lett.*, vol. 104, no. 23, 2014.

- [13] J. C. Park, H.-N. Lee, and J. Chul, "Dry etch damage and recovery of gallium indium zinc oxide thin-film transistors with etch-back structures," *Displays*, vol. 33, no. 3, pp. 133–135, 2012.

- [14] S. Walther, S. Polster, B. Meyer, M. P. M. Jank, H. Ryssel, and L. Frey, "Properties of SiO2 and Si3N4 as gate dielectrics for printed ZnO transistors," *J. Vac. Sci. Technol. B Microelectron. Nanom. Struct.*, vol. 29, no. 1, p. 01A601, 2011.

- [15] S. M. Jejurikar, M. M. De Souza, and K. P. Adhi, "Understanding the role of the insulator in the performance of ZnO TFTs," *Thin Solid Films*, vol. 518, no. 4, pp. 1177–1179, 2009.

- [16] E. Kim *et al.*, "Influence of the charge trap density distribution in a gate insulator on the positive-bias stress instability of amorphous indium-gallium-zinc oxide thin-film transistors," *Appl. Phys. Lett.*, vol. 108, no. 18, pp. 1–6, 2016.

- [17] Z. Sisman, S. Bolat, and A. K. Okyay, "Atomic Layer Deposition for Vertically Integrated ZnO Thin Film Transistors: Toward 3D High Packing Density Thin Film Electronics," *Phys. status solidi c*, vol. 14, no. 9, p. 1700128, 2017.

- [18] Y. S. Chun, S. Chang, and S. Y. Lee, "Effects of gate insulators on the performance of a-IGZO TFT fabricated at room-temperature," *Microelectron. Eng.*, vol. 88, no. 7, pp. 1590–1593, 2011.

- [19] L. Yuan, X. Zou, G. Fang, J. Wan, H. Zhou, and X. Zhao, "High-Performance Amorphous Indium Gallium Zinc Oxide Thin-Film Transistors With HfO x N y / HfO 2 / HfO x N y Tristack Gate Dielectrics," *IEEE Electron Device Lett.*, vol. 32, no. 1, pp. 42–44, 2011.

- [20] S. Y. Lee, D. H. Kim, E. Chong, Y. W. Jeon, and D. H. Kim, "Effect of channel thickness on density of states in amorphous InGaZnO thin film transistor," *Appl. Phys. Lett.*, vol. 98, no. 12, 2011.

- [21] Y. Li *et al.*, "Effect of channel thickness on electrical performance of amorphous IGZO thin-film transistor with atomic layer deposited alumina oxide dielectric," *Curr. Appl. Phys.*, vol. 14, no. 7, pp. 941–955, 2014.

- [22] M. G. Yun, S. H. Kim, C. H. Ahn, S. W. Cho, and H. K. Cho, "Effects of channel thickness on electrical properties and stability of zinc tin oxide thin-film transistors," *J. Phys. D. Appl. Phys.*, vol. 46, no. 47, 2013.

- [23] E. N. Cho, J. H. Kang, and I. Yun, "Effects of channel thickness variation on bias stress instability of InGaZnO thin-film transistors," *Microelectron. Reliab.*, vol. 51, no. 9–11, pp. 1792–1795, 2011.

- [24] J. Li, X. W. Ding, J. H. Zhang, H. Zhang, X. Y. Jiang, and Z. L. Zhang, "Improving electrical performance and bias stability of HfInZnO-TFT with optimizing the channel thickness," *AIP Adv.*, vol. 3, no. 10, pp. 1–8, 2013.

- [25] C. Choi, Y. Baek, B. M. Lee, K. H. Kim, and Y. S. Rim, "Enhanced electrical stability of nitrate ligand-based hexaaqua complexes solution-processed ultrathin a-IGZO transistors," J. Phys. D. Appl. Phys., vol. 50, no. 48, 2017.

# **Chapter I**

# History and physics of thin film transistors

#### **I.1 Introduction**

This chapter introduces the thin film transistor (TFT) history and its development decade by decade until nowadays. After that the physics of metal insulator semiconductor (MIS) is explained. TFT is a type of MIS device. At this section we explain and modulate the phenomena in MIS structure which explain how transistor works.

#### I.2 History of thin film transistors

The research on thin films transistors started about 80 years ago. It was in that time the understanding about semiconductors become clearer. In this section, decade by decade, how the thin-film transistor has evolved in materials and structure to the forms most widely used today will be reviewed.

#### I.2.1 Field effect device

The idea of the field effect device started in 1930s with a patent of J.E Lilenfeld [1]–[3] and O. Hei [4]. They suggested a device for controlling an electric current by a voltage. The problem is that no clear idea on how this is this device working of as they failed in describing the invention due to misunderstanding of semiconductors in this period of time.

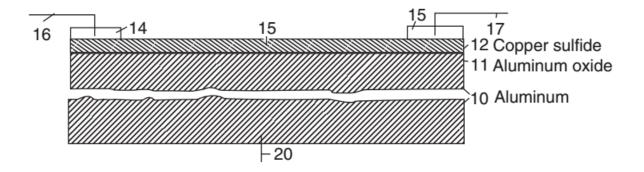

The patent of J.E Lilenfeld and O. Heil shown in Figure I-1 and Figure I-2 respectively They use Copper Sulfide (CuS) as the active layer, Aluminum(Al) as electrodes and Aluminum Oxide  $(Al_2O_3)$  as insulator which has a thickness of about 100 nm. However, this TFT never worked because the thickness of the insulator is quite thick.

Figure I-1 Diagram of the first field-effect electronic device.

Figure I-2 Diagram of an early field-effect device.

As it is normal with many innovations at that time, its practical realization was delayed until adequate materials and technologies were available for its fabrication. It can be even said (and for most it could be surprising) that the TFT was the first solid-state amplifier ever patented [5], [6].

The work of Shockley on semiconductors and the discovery of the point-contact transistor by Bardeen and Brattain in late 1947 has led to the creation of the first filed effect transistor in 1952. Shockley was able to explain the phenomena of field effect on semiconductors materials. The TFT as everyone knows it today really began with the work of P. K. Weimer at RCA Laboratories in 1962 [7]. He used thin films of polycrystalline Cadmium Sulfide (CdS) as active layer. The thin film of CdS was deposited by evaporation on a glass substrate, while source, drain and gate contacts are formed by evaporation. Silicon monoxide thin film of insulator is interposed between the gate electrode and the semiconductor. This CdS TFT structure is shown in Figure I-3

Figure I-3 TFT structure of Weimer's top-gate staggered CdS TFT structure.

The threshold behavior of Weimer's TFTs suggested a fairly large density of interface states. This density was estimated at  $10^{12}$ – $10^{13}$  cm<sup>-3</sup>. In 1964 Weimer [8] reported *p* channel TFTs made with tellurium as the active material. On the theoretical side, Borkan and Weimer published in 1936 [9] their analysis of TFT characteristics. As mentioned earlier, this was based upon Shockley analysis of the JFET, which is now known as the gradual channel approximation.

### **I.2.2 TFT based on** a - Si: *H* and poly crystal Si

The work of Lecnher et al [10] was a big motivation for research on TFT. They have used TFTs to control the pixel of a liquid crystal displays (LCD), obtaining considerably less crosstalk, lower response time and higher contrast ratios than that achieved when controlling liquid crystals with more conventional x - y disposed electrodes. By this time, the display applications of TFTs were motivating the work of most groups. As a result, efforts were increasingly focused on the issues of stability and ON/OFF ratio, as well as OFF current, or leakage. Stability was a serious

issue. CdSe is a polycrystalline compound; its properties are influenced by grain size, grain boundary interface states, stoichiometry, etc., and it can be sensitive to ambient gases such as  $H_2O$ and oxygen. From this time a big debate as to which material was best suited for use in TFTs for most important application such as in liquid crystal displays has started.

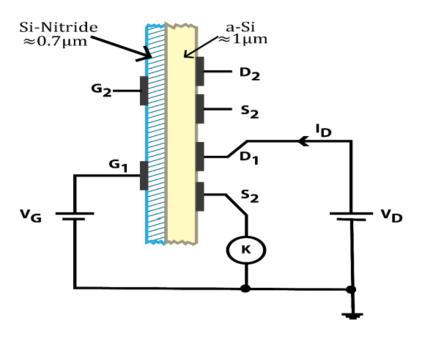

Le Comber, Spear, and Ghaith used amorphous silicon (a-Si) as active layer for thin films transistor [11]. Figure I-4 shows the structure of first with a-Si TFT.

Figure I-4 First TFT with a-Si like active layer

The high concentration of defects in a-Si makes its TFTs having poor characteristics but it is promising for application on LCD. The hydrogenated amorphous silicon (a-Si:H), in contrast to pure amorphous silicon (a-Si) has higher mobility and is stable in the atmosphere [12]. Those properties make a-Si:H the material for next decade in TFT application. a-Si:H is perfectly suitable for the application of TFTs as switching elements in LCDs, since it has low cost, good reproducibility and uniformity in large areas and *on/off* exceeding 10<sup>6</sup>a, threshold voltage ( $V_{th}$ ) of < 3 V, and a subthreshold slope (S) of < 0.5 V/dec [13]. In 1982, both IBM group [14] and Nishimura et al [15] using Polycrystalline silicon (Poly-Si) as channel on TFTs in LCD. Poly-Si TFTs have field-effect mobility ( $\mu_{FE}$ ) hundreds of times higher than that of a-Si TFTs and exhibit great performance. The development of poly-Si TFTs for displays started with the realization of low temperature poly-Si TFTs, based on molecular beam epitaxy (MBE) technology by Matsui and co-worker [16]. They fabricated TFTs on a glass substrate at a low temperature of below 610 °C.

#### I.2.3 Organic TFT

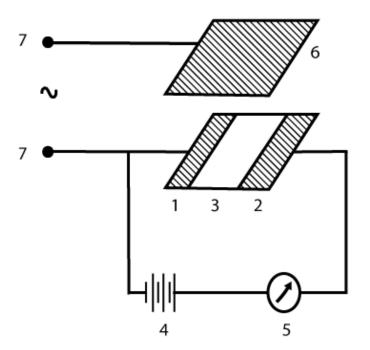

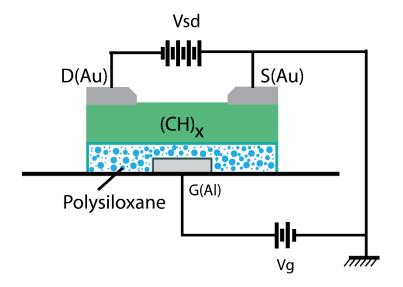

Conventional electronics is based on inorganic semiconductors such as germanium, silicon or Gallium arsenide. Organic materials like plastics are usually associated with electrical insulation. In the 1960s it was discovered that some organic materials can carry an electric current [17], [18]. In the beginning, Organic conductive materials were applied in xerographic devices (photocopiers) [19]. The work Shirakawa and all stimulated the research in organic when they found that the electrical conductivity of polymer semiconductor could be higher and closer to a-Si [20]. The first application of organic material on TFT was reported in the literature in 1983 [21]. Figure I-5 shows the structure of an organic TFT.

Figure I-5 the first Organic thin films transistor

The active organic material in the middle is called organic semiconductor. An organic semiconductor consists of aggregates of organic molecules bound by weak van der Waals forces. These molecules contain loosely bound  $\pi$ -electrons that are ultimately responsible for electrical

conduction [22]. There are several organic materials used as the active semiconducting layer, including small molecules such as rebrene, tetracene, pentacene, diindenoperylene, perylenediimides, tetracyanoquinodimethane (TCNQ), and polymers such as polythiophenes (especially poly 3- hexylthiophene (P3HT)), polyfluorene, polydiacetylene, poly 2,5-thienylene vinylene, poly p-phenylene (PPV). Organic TFTs made of small organic molecules, such as pentacene, have better characteristics than those made of large molecule polymers [23]. Organic materials can be n-type or p-type. The properties of organic semiconductors in general, can be tuned by changing their chemical composition. Mechanical properties; suitable for flexible applications; can be adjusted. Polymer can be made strong; flexible, lightweight. Organic material can be processed at low temperatures, typically below 150°C, compatible with most type of substrates and can use cheap and large-scale methods like inkjet printing, spin coating, roll-to-roll to fabricate organic electronic circuits. This later make the cost of production lower [24]. The challenge for researcher in the field of organic semiconductors is to increase the low mobilities, solve the major rapid oxidation in the air. The stability of the organic TFT in the atmosphere is another common concern, the metallic electrodes is another problem due to low melting point of organic materials. Thin films of organic semiconductors are not heat durable, organic TFT have high threshold voltage  $V_{th}$  of about 15 V, For that all these reasons, commercial applications of organic TFTs is very limited [25].

#### I.2.4 Transparent Oxide Semiconductors TFT

Transparent conducting oxide (TCOs) is an unusual class of materials possessing two physical properties: high optical transparency (more than 80%) in the visible region. high electrical conductivity (about  $10^3 \Omega^{-1} cm^{-1}$  or more). The first is due to the material large energy band gap of about 3.0 *eV* while the last is because of high concentration of electrical carries (electron or hole) about  $10^{19} cm^{-3}$ , with a sufficiently large mobilities  $> \sim 1 cm^2 V^{-1} S^{-1}$ . The TCO are considered to be good conductors compared to semiconductors, while they are actually very poor conductors compared to metals. They are also called transparent semiconducting oxides TSO [26], [27]. The properties and stability of TSO on atmosphere attracted several academic and industrial groups. The first application of TFT in which TSO is used as a channel layer was in 1964, when  $SnO_2$  is evaporated on a glass substrate with aluminum source-drain and gate electrodes,  $Al_2O_3$  was used as a gate dielectric. Figure I-6 shows the  $SnO_2$  TFT structure[28]. Later on; *ZnO* was used as TSO channel lyre for TFT [29].

Figure I-6. The first TFT based on SnO<sub>2</sub>

The first generation of TFTs based on TSO had very poor output characteristics. In 2001 the work of Ohya et al achieved good  $I_{on}$  value but the problem was with saturation [30]. The revolution of transparent transistors based on oxide semiconductors was in 2003 when Hoffman et al, Carcia et al and Masuda et al [31]–[33] obtained results for ZnO TFT comparable or even superior to a-Si:H and organic TFTs. The advantage of ZnO is the good properties obtainable by non-vacuum methods and on low temperature or room temperature process [34]–[36].

The first modeling and simulation of polycrystalline ZnO thin films transistor helped in discovering large properties of the TSO polycrystalline structure[37]. There are other TSO used as an active layer in TFT such as  $In_2O_3$  and  $SnO_2$  [38], [39].  $ZnO_2$  got eventually the upper hand due to its abundance and low cost. Binary polycrystalline n-type TSO like ZnO and  $SnO_2$  are sensitive to environmental atmospheres because of adsorption of oxygen species on the surface/grain boundaries (GBs) which act as traps for electrons. Long term stability plus high cost for large scale production are a big obstacle for industry and commercialization. Issues like degradation in mobility and stability are probably due to GB issues.

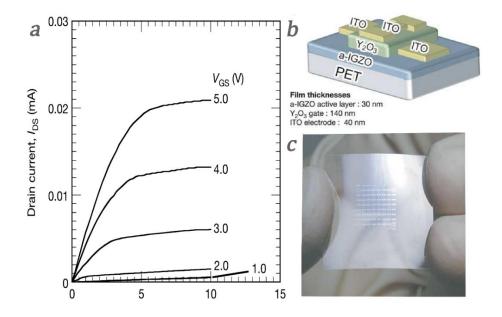

In 2003 Nomura et al introduced a new type of TSO by using complex  $InGaO_3(ZnO)_5$  or IGZO single crystalline semiconductor layer as channel in TFT [40]. This layer was epitaxially grown on an yttria stabilized zirconia substrate and has achieved a spectacular result: turn on voltage of -0.5 V, On/Off ratio of  $10^6$  and effective mobility about 80  $cm^2V^{-1}s^{-1}$ . To attain this

level of performance high temperature of about  $1400^{\circ}C$  was required. It turns out that this publication attracted huge attention and opened new field of research on multicomponent oxide semiconductors. One year later Nomura et al made history, when they obtained high performance of TFT based on amorphous IGZO, depositing near room temperatures by pulsed laser deposition (PLD) on flexible substrates [41]. Figure I-7 shows  $I_{DS} - V_{DS}$  curves and structure of a-IGZO TFT on flexible substrate.

Figure I-7. The first a-IGZO deposited at room temperature by Nomura et al. a)  $I_{DS} - V_{DS}$  curve b) structure of a-IGZO TFT c) the flexible substrate

Even a-IGZO showed lower performance compared with single crystalline TFTs, but a-IGZO TFT still having good performance with  $\mu_{sat} = 9 \ cm^2 V^{-1} s^{-1}$ ,  $V_T \approx 1 - 2 V$  and  $\frac{On}{off} \approx 10^3$ . These results are superior than a - Si: *H* ororganic semiconductors. This proved the low sensitivity of multicomponent oxide to structural disorder; in other word the multicomponent oxides are the future material for TFT application. Nowadays a-IGZO has receive great importance in research and development to achieve high performance with non-vacuum methods, lower the cost of large areas devices and long term of stability.

### I.3 Physics and modeling TFTs

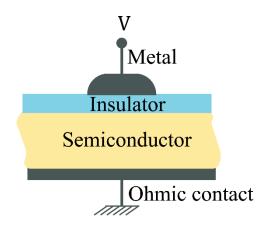

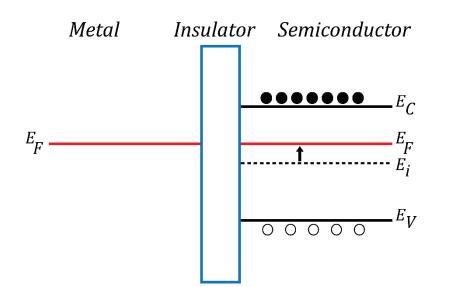

Thin film transistors (TFT) is field effect device, the heart of field effect devices is contact metal-insulator-semiconductor MIS, the MIS device is most useful devices to describe semiconductor surface. In this section we concentrate on MIS system to understand the physics phenomena which happen on ideal MIS. The Figure I-8 presents structure of simple MIS device where The Insulator between metal and semiconductor and V is applied voltage. this device show similarity with capacitor for that it is also known MIS capacitor.

Figure I-8 Metal Insulator Semiconductor system

### I.3.1 Ideal MIS Capacitor structure

Figure I-9 shows the band diagram of an ideal MIS capacitor, on a n-type substrate, in which the Fermi levels in the metal and in the semiconductor perfectly align, such that there is no induced band bending within the structure. In the analyses below, the following conventions will be used: The Fermi potential,  $V_F$ , will be measured from the bulk intrinsic level,  $E_i$ , and will be taken as positive below  $E_i$  and negative about it. Similarly, the band bending,  $V_S$ , will be measured from the bulk intrinsic level,  $E_i$ .

Figure I-9 Energy-band diagrams of ideal MIS capacitors at equilibrium (V = 0)

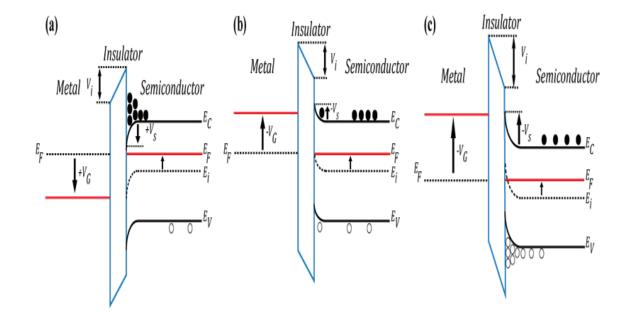

When a positive charge,  $Q_G$ , is placed on the metal gate, it will induce an equal and opposite negative charge in the semiconductor,  $Q_s$ , and this negative charge will consist of an increase in the electron density, due to an increase in the free electrons density. This is associated with bending downwards by an amount  $+V_s$ . In this case, the surface is said to be *accumulated* Figure I-10 (a) shows the accumulated state. With a negative bias applied to gate, there is an increase in the positive charge in the semiconductor and a decrease in the free electrons density, thereby, leaving behind immobile, ionized donor centers,  $N_d$ . In order to accommodate these charges in free carries density, the bands within the semiconductor will have to bend upwards near its surface, as shown Figure I-10 (b). It will also be seen that the negative charge on the gate results from a negative bias being applied to the gate relative to the semiconductor. Following the convention discussed above, the Fermi level in the metal is moved upwards in response to a negative gate bias,  $V_G$ , and the semiconductor surface potential is  $-V_s$ . The situation shown in the diagram is for a small negative compared with  $N_d$ , and surface is said *depleted* (of free electron). For a lager positive gate bias, the situation shown in Figure I-10 (c) occurs. In this case, there is a corresponding increase in the band bending,  $V_s$ , and the free hole concentration at the surface is larger than  $N_d$ . The surface is now said to be *inverted*. Between these two situations, when the band bending,  $V_s = V_F$ , the surface

will be intrinsic, and  $n_s = p_s = n_i$ . Further negative band bending beyond this point will lead to  $n_s < p_s$ .

Figure I-10 Energy-band diagrams for ideal MIS capacitors under different bias conditions: (a) accumulation, (b) depletion, and (c) inversion. The semiconductor substrate is n-type.

With a p-type substrate, the opposite situation occurs. Negative bias leads to accumulation, and positive bias causes the surface depleted/ inverted. To find the relationship between  $V_s$  and  $Q_s$  and  $V_G$ , it is necessary to solve Poisson's equation, thus

$$\frac{d^2V}{dx^2} = -\frac{q\rho(x)}{\varepsilon_0\varepsilon_s}$$

I-1

$\varepsilon_0$  is the vacuum permittivity,  $\varepsilon_s$  is the semiconductor, dielectric constant.(*x*) is the space charge density, given by:

$$\rho(x) = p(x) - n(x) + N_d \qquad I-2$$

The free carrier densities are defined by the intrinsic carrier concentration,  $n_i$ , and the separation of the Fermi level from the intrinsic level, i.e.:

$$p(x) = n_i exp\left(\frac{q(V_F - V)}{kT}\right)$$

I-3

$$n(x) = n_i exp\left(\frac{-q(V-V_F)}{kT}\right)$$

I-4

$$p(x) - n(x) = 2n_i sh\left(q \frac{V_F - V}{kT}\right)$$

I-5

Where T is the temperature, and k is Boltzmann's constant. At the surface,  $V = V_s$ , and the in the bulk, where V = 0:

$$\begin{cases} p_0 = n_i exp\left(\frac{qV_F}{kT}\right)\\ n_0 = n_i exp\left(\frac{-qV_F}{kT}\right) \end{cases}$$

From charge neutrality,

$$n_0 - p_0 = N_d = 2n_i sh\left(q \frac{V_F}{kT}\right)$$

I-6

$$\frac{d^2V}{dx^2} = -\frac{2n_i q}{\varepsilon_0 \varepsilon_s} \left\{ sh\left(\frac{q(V_F - V)}{kT}\right) - sh\left(\frac{qV_F}{kT}\right) \right\}$$

I-7

Using  $\frac{d^2V}{dx^2} = \frac{1}{2} \frac{d}{dV} \left(\frac{dV}{dx}\right)^2$ , and integrating equation I-7 from the bulk (V = 0, and  $\frac{dV}{dx} = 0$ ) to the surface( $V = V_s$ , and  $\frac{dV}{dx} = -F_s$ ):

$$\left(\frac{dV}{dx}\right)^{2}_{V=V_{S}} \equiv F_{S}^{2} = \frac{4n_{i}q}{\varepsilon_{0}\varepsilon_{s}} \left\{\frac{kT}{q} ch\left(\frac{q(V_{F}-V_{S})}{kT}\right) - \frac{kT}{q} ch\left(\frac{qV_{F}}{kT}\right) + V_{S}sh\left(\frac{qV_{F}}{kT}\right)\right\}$$

I-8

From Gauss' Law, the surface field,  $F_s$ , is related to the total areal charge,  $Q_s$ , contained within the surface by:

$$Q_s = -\varepsilon_0 \varepsilon_s F_s \qquad \qquad I-9$$

Hence, the relationship between  $Q_s$  and  $V_s$  is given by

$$Q_s = \pm \sqrt{4n_i q \varepsilon_0 \varepsilon_s} G(V_s, V_F)$$

I-10

Where  $G(V_s, V_F)$  is given by:

$$G(V_S, V_F) = \mp \sqrt{\left\{\frac{kT}{q} ch\left(\frac{q(V_F - V_S)}{kT}\right) - \frac{kT}{q} ch\left(\frac{qV_F}{kT}\right) + V_S sh\left(\frac{qV_F}{kT}\right)\right\}}$$

I-11

Given the positive and negative values of  $Q_s$  in equation *I-10*, the appropriate sings of  $V_s$ ,  $F_s$  and  $Q_s$  are given in Table I-1, and the correct value of  $Q_s$  is given by:

$$Q = -\frac{V_s}{|V_s|} |Q_s| \qquad I-12$$

Table I-1: Polarity relationship between band bending, surface field and space charge in an MIS

| V <sub>s</sub> | $F_{s}$ | $Q_s$ | Free carrier conditions                        |

|----------------|---------|-------|------------------------------------------------|

| -Ve            | -Ve     | +Ve   | Reduction of electrons and/or increase of hole |

| +Ve            | +Ve     | -Ve   | Reduction of hole and/or increase of electrons |

When the volume concentration of free electrons at the surface,  $n_s$  is equal to the volume concentration of acceptors  $N_a$  ( $V_s = V_F$ ), the surface is intrinsic ( $n_s = p_s = n_i$ ), and the band bending regime beyond this, and up to strong inversion, is referred as weak inversion ( $p_s < n_s < N_a$ ).

In the depletion/inversion regime, the band bending  $V_s$  is positive, and for  $V_s$  and  $V_F > KT/q$ , i.e., more than KT from the flat band position, equation.10 can be simplified to

$$Q_{s} \simeq -\sqrt{2q\varepsilon_{0}\varepsilon_{s}} \left\{ n_{i} \frac{kT}{q} \exp\left(\frac{q(V_{s}-V_{F})}{KT}\right) + N_{a}V_{s} \right\}^{0.5}$$

$$I-13$$

The first term in brackets relates to the free electron concentration and the second term to the ionized acceptor space charge density. When the ionized acceptor space charge dominates equation 13 can be further reduced to

$$Q_s \cong -\sqrt{2q\varepsilon_0\varepsilon_s N_a V_s} \equiv Q_b \qquad \qquad I-14$$

Where  $Q_b$  is the areal acceptor space charge den<sub> $\varepsilon$ </sub> sity. Equation I.14 is the same as directly calculated from Poisson's equation using the depletion approximation, i.e. from

$$\frac{d^2 V}{dx^2} = \frac{q N_a}{\varepsilon_0 \varepsilon_s}$$

I-15

And integrating this with respect to x or if equation I.15 is integrated with respect to V, then:

$$Q_s = -qN_a x_d I-16$$

Where  $x_d$  is the width of the space charge depletion region at  $V_s$ . At inversion when  $V_s = 2V_F$ , further increase in the band bending causes such large increase in  $Q_s$ , due to exponentially increasing free electron density. To a first approximation, the fixed space charge can be regarded as having reached a limiting maximum value,  $Q_{max}$ . This can be obtained by substituting  $V_s = 2V_F$  into equation I.14

$$Q_{bmax} = -\sqrt{2q\varepsilon_0\varepsilon_s N_a 2V_F} \qquad \qquad I-17$$

And from equation I.16

$$Q_{bmax} = -qN_a x_{dmax} I-18$$

Where  $x_{dmax}$  is the maximum width of the depletion region, and, from equation I-18 and I-19,  $x_{dmax}$  is given by:

$$x_{dmax} = \sqrt{\frac{2\varepsilon_s \varepsilon_s 2V_F}{qN_a}}$$

I-19

$Q_s$  in equation I.13 can be represented by the sum:

$$Q_s = Q_n + Q_b I-20$$

Where  $Q_b$  is the extended depletion layer charge, and  $Q_n$  is the areal density of inversion layer electron.

#### I.3.2 Gate bias and threshold voltage

Back to Figure I-10, the gate voltage,  $V_G$  is dropped partially across the dielectric,  $V_i$  and partially across the semiconductors,  $V_s$  so that:

$$V_G = V_i + V_s I-21$$

And for charge neutrally, the charge on the gate,  $Q_G$ , equals the charge in the semiconductors  $Q_s$ and

$$Q_G = \varepsilon_0 \varepsilon_i F_i = \varepsilon_0 \varepsilon_i \frac{V_i}{d_i} = C_i V_i = -Q_s$$

I-22

Where  $F_i$  is the field in the gate dielectric, and  $C_i$  is the capacitance/unit area of the gate dielectric. Hence

$$V_G = V_s - \frac{Q_s}{C_i}$$

I-23

Equation I.23 can be used to relate the voltage on the gate of an MIS capacitor to the induced charge density in the semiconductor,  $Q_s$  and to the associated band bending,  $V_s$ . It can also be used to calculate the threshold voltage,  $V_{th}$  of the structure i.e the gate voltage necessary to induce band bending of  $2V_F$  at the semiconductor surface:

$$V_{th} = 2V_F + \frac{\sqrt{2q\varepsilon_0\varepsilon_i N_a 2V_F}}{c_i}$$

I-24

For the real behavior the work function influence and fixed charge in insulators and charge in the interface have to be taken inti account to properly establish the threshold formula

$$V_{th} = 2V_F + \frac{\sqrt{2q\varepsilon_0\varepsilon_i N_a 2V_F}}{C_i} + V_{FB} + \frac{Q_{SS}(V_S = 2V_F)}{C_i}$$

I-25

$Q_{ss}$  is charge in semiconductor surface. A at inversion is given by:

$$Q_{ss}(A) = qN_{ss}q(2V_F - V_F) = qN_{ss}qV_F$$

I-26

Where  $V_{FB}$  equal

$$V_{FB} = \Phi_{MS} - \frac{Q_{ieff}}{c_i} - Q_{ss}(V_s = 0) / C_i$$

I-27

$\Phi_{MS}$  is metal–semiconductor work function difference.  $Q_{ieff}$  is effective charge. will be determined, as though it were located at the dielectric/semiconductor interface.

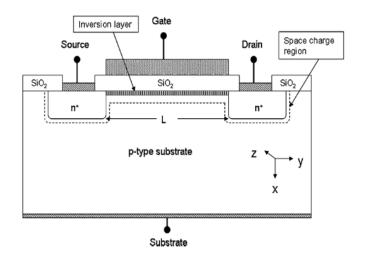

#### I.3.3 MOSFET operation

Figure I-11 shows a schematic diagram of an n-channel MOSFET, in which there are  $n^+$  doped source and drain regions, separated by a distance L, which defines the channel length. The width of the channel W, is in the z-direction (which is perpendicular to the page). Surface band bending, perpendicular to the *Si/SiO*<sub>2</sub> interface, is in the x-direction. In the on state, positive biases  $V_D$  and  $V_G$  are applied to the drain and gate contacts, respectively, with respect to the ground source contact. There is a fourth contact in MOSFET, which is the p-type substrate connection, which is

under reverse bias. For TFT, this connection to the device layer will generally not be available. The device to be described is the long channel model, in which the field along the channel (control of the on current) is much smaller than the vertical field (determining the inversion layer concentration), and the two are effectively decoupled. This means that 2D phenomena is to be considered. The band bending and energy level conventions are those used in MOS.

Figure I-11. 2 D illustration cross section of a MOSFET

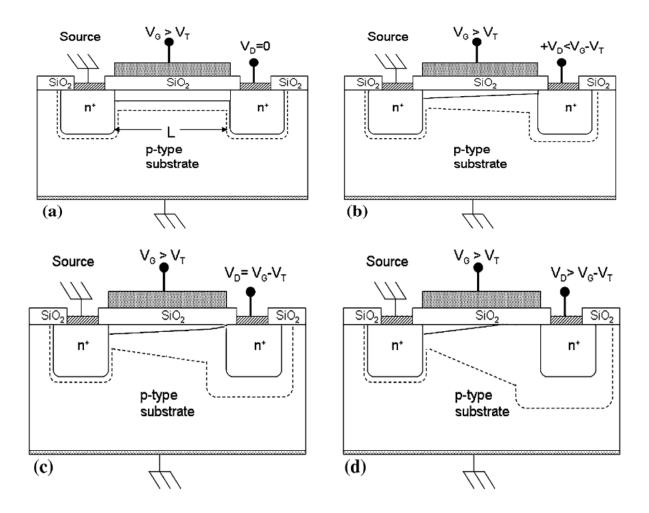

The first situation shown in the Figure I-12.a, in which there is an inversion layer induced by the gate bias, V<sub>G</sub> (larger than V<sub>T</sub>), and at zero drain bias, the inversion layer will be uniform along the channel. The real charge densities within an inverted surface can be represented by the free electron inversion charge density,  $Q_n$  and the underlying ionized acceptor space charge density,  $Q_b$  where  $Q_n$ ,  $Q_b$  and  $V_T$  are given by:  $Q_n = C_i(V_G - V_T)$ ,  $Q_b = qN_a x_{damx} = \sqrt{(2q\varepsilon_0\varepsilon_s N_a 2V_F)}$ ;  $V_T = 2V_F + \sqrt{(2q\varepsilon_0\varepsilon_s N_a 2V_F)}/C_i$

Positive bias,  $+V_D$  applied to the drain contact will reverse the  $n^+$  drain region with respect the ptype substrate, and the current flow between the two is limited to the leakage current of the junction.

When the drain bias,  $V_D$  is low (i.e less than  $V_G - V_T$ ), then  $V_D$  will be uniformly dropped along the channel inversion layer, resulting in both a constant field  $V_D/L$  and the flow an ohmic electron current,  $I_d$  between the source and drain contacts. This is defined as the linear regime of

device behavior. As  $V_D$  is increased, the ohmic channel current increases, and eventually,  $V_D$ reaches a value where, is still less than  $V_G - V_T$ . As this happens, the potential at the drain end the channel needs to be considered when computing the inversion charge density along the channel. For instance, at the drain end of the channel, the voltage drop across the oxide between the inversion layer and the gate electrode is now  $V_G - V_T - V_D$ , while it remains at  $V_G - V_T$  at the source end to maintain current continuity. There will be a corresponding field redistribution along the channel, it increases more at the drain than the source as  $V_{DS}$  is increased. The current now no longer increase linearly with  $V_D$ , but becomes sub-linear. This situation is shown in Figure I.12b. In addition, in order to maintain charge neutrality between the charge on gate,  $Q_G$  and the charge in the semiconductor, the reduction in  $Q_n$  will be balanced by an increase in  $Q_b$  such that the thickness of the ionized acceptor space charge layer increases beyond the thermal equilibrium value of  $x_{dmax}$  (equation 19). This is shown qualitatively, in Figure I.12.b. Hence, for the depletion width to increase beyond this value, the amount of band bending has to increase beyond  $2V_F + V_D$ at the drain. The qualitative changes in the charge distribution and the band bending, is at the source and drain ends of the channel. The bias at the drain results in a non-thermal equilibrium situation, with the thermal equilibrium Fermi level splitting in separate hole and electron quasi Fermi levels,  $E_{Fp}$  and  $E_{Fn}$ , respectively which are separated by  $V_D$ . Hence, this diagram shows physically why the band bending,  $V_s$ , must increase to  $2V_F + V_D$  at drain: it is to bring the intrinsic level at the surface to  $qV_F$  below the electron quasi-Fermi level at the drain. This is the condition required to invert the p-type surface of a reverse-biased gated  $n^+ - p$  diode. This is the direct analogue of the thermal equilibrium situation, in which inversion occurs when the intrinsic level is  $qV_F$  below the equilibrium Fermi level.

Finally, as shown in Figure I-12.c, when  $V_D = V_G - V_T$ ,  $Q_n$  is reduced to zero at the drain and channel is *pinched-off*. However, as all electrons arriving at the edge of the drain space charge region are swept through into the drain, this does not pinch-off the current, but it saturates, and the device operation moves into the *saturation regime*. The voltage at which this happen is the *saturation voltage*,  $V_{Dsat}$ . The current saturation occurs because, in principle, the maximum possible potential difference,  $V_{Dsat}$ , has been dropped along the channel, and the pinch-off voltage remains at  $V_{Dsat}$  even when  $V_D$  is increased. However, in reality, as  $V_D$  is increased the drain space charge region grows and the pinch-off point moves towards the source. Hence, even though the total voltage drop along the channel remains at  $V_{Dsat}$ , the effective channel length shortens, and the mean channel field increases. This is show in Figure I.12d and this increase in field leads to a corresponding increase in the saturation current. Since pinch-off occurs at  $V_D = V_{Dsat} = V_G - V_T$ , increasing  $V_G$  leads to a corresponding increase in  $V_{Dsat}$ . This makes the saturation current to increase as  $(V_G - V_T)^2$ , due to the correlation of  $V_{Dsat}$  with  $V_G$ .

Figure I-12 Cross-section of MOSFET, in the on-state, for different values of drain bias  $V_D$ : a)  $V_D = 0$ , b)  $V_D < V_G - V_T$ , c) at pinch-off, with  $V_D = V_G - V_T = V_{D(sat)}$ , and d)  $V_D > V_{D(sat)}$  showing channel shortening.

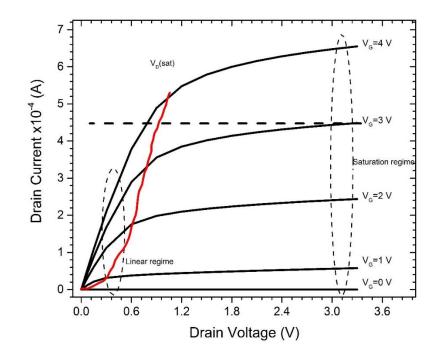

The MOSFET output characteristics in Figure I.13 illustrate the key features described above: in particular, the linear and saturation regimes, the increasing values of the saturation voltage,  $V_{Dsat}$ , with increasing  $V_G$ .

Figure I.I-13. Measured MOSFET output characteristics showing the linear and saturation operating regimes.

#### I.3.4 Current-Voltage modulation

As shown the Figure I.12 b-d, the current density  $J_D$  at any point x, y in the channel given by:

$$J_D = \sigma_n(x, y)F(y) \qquad I-28$$

Where y is the direction of current flow, x is the direction perpendicular to the  $Si/SiO_2$  interface,  $\sigma_n$  is the local electron conductivity, and F is the local field in the direction of current flow. The conductivity,  $\sigma_n$  is given by:

$$\sigma_n(x, y) = q\mu_n n(x, y)$$

I-29

The current  $I_d(y)$  at a position y is given by the integration the electron density, *n* over the depth of the channel and across the width the channel *W*

$$I_{d}(y) = W \int_{0}^{x_{i}} \sigma_{n}(x, y) F(y) = -W \int_{0}^{x_{i}} q \mu_{n} n(x, y) \frac{dV(y)}{dy} dx$$

I-30

$$I_d = -Wq\mu_n \frac{dV(y)}{dy} \int_0^{x_i} (x, y) dx \qquad I-31$$

Where it is assumed that the electron mobility is independent of the field in both the x and y directions and V(y) is the potential in the channel at a point y. For an inverted surface the areal charge in the inversion layer can represented by  $Q_n$  where  $Q_n$  is the integral of the volume electron concentration through the depth of the channel

$$Q_n(y) = q \int_0^{x_i} n(x, y) dx \qquad I-32$$

$Q_n$  is also related to gate bias  $V_G$  by:

$$Q_n(y) = -C_i [V_G - V_T - V(y)]$$

I-33

By replacing the  $Q_n$  formula in equation 34

$$I_{d} = -\mu_{n}W \frac{dV}{dy}Q_{n}(y) = \mu_{n}W \frac{dV}{dy}C_{i}[V_{G} - V_{T} - V(y)]$$

I-34

Integrating y along the channel from 0 to L and V(y) from 0 to  $V_D$

$$\int_{0}^{L} I_{d} d_{y} = \mu_{n} W C_{i} \int_{0}^{V_{D}} \{ V_{G} - V_{T} - V(y) \} dv$$

I-35

For current continuity  $I_d$  is independent of position within the channel, hence:

$$I_d = \frac{\mu_n W C_i}{L} \{ (V_G - V_T) V_D - 0.5 V_D^2 \}$$

I-36

This is the classical, simplified MOSFET equation, which is widely used to interpret TFT behavior

#### Linear Regime

For  $V_D \ll V_G - V_T$  equation I.36 reduces to

$$I_d = \frac{\mu_n W C_i (V_G - V_T) V_D}{L}$$

I-37

This equation describes the current-voltage characteristics in the linear regime.

#### **Saturation Regime**

For  $V_D V_G - V_T = V_{Dsat}$  the current saturation at  $I_{dsat}$  and equation 35 reduces to:

$$I_{dsat} = \frac{\mu_n W C_i (V_G - V_T)^2}{2L} \equiv \frac{\mu_n W C_i V_{Dsat}^2}{2L}$$

I-38

Hence, in saturation the current increases quadratically with  $V_G - V_T$  because the inversion charge increase by this amount, as does the maximum potential drop along the channel.

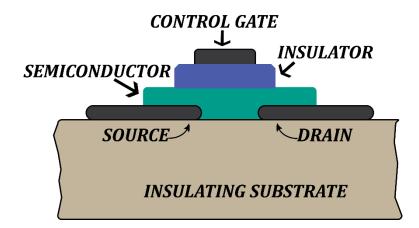

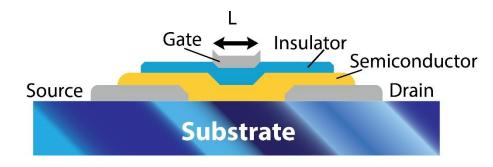

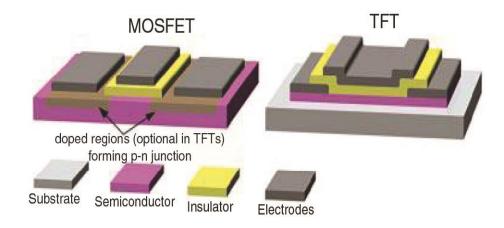

#### I.4 Thin film Transistor

Thin film transistor is a kind of MOSFET. That is it has a similar structure to MOSFET. The difference between TFT and MOSFET is that the active layer can be any type of semiconductor and the active layer is deposited as a thin film on a different material substrate (glass for example) as shown in Figure I.14. Because the semiconductor layer is formed by deposition, the material has more defects and imperfections than in single crystalline semiconductor. The transport processes become complicated in TFT. In a TFT, the leakage current is always higher due to defects, the current is limited resulting in a lower mobility. To improve device performance, reproducibility, and reliability, the bulk and interface trap densities must be reduced to reasonable levels.

Figure I-14 Schematics showing show the difference between MOSFET and TFT

In addition, MOSFETs have p-n junctions at the source-drain regions, which are absent in TFTs. This is another important difference in device operation: even if both TFTs and MOSFETs rely on the field effect to modulate the conductance of the semiconductor close to its interface with

the dielectric. In TFTs this is achieved by an accumulation layer, while in MOSFETs an inversion region has to be formed close to that interface, i.e., a n-type conductive layer is created in a p-type silicon substrate (inversion) [42].

#### **I.5 References**

[1] J. E. Lilienfeld, "US Patent# 1,745,175," *January 18th*, 1930.

[2] L. J. Edgar, *Amplifier for electric currents*. Google Patents, 1932.

[3] L. J. Edgar, "Device for controlling electric current," Mar. 1933.

[4] O. Heil, "British Patent 439 457," *Appl. Filed*, vol. 4, 1935.

[5] W. Shockley, "The Theory of p-n Junctions in Semiconductors and p-n Junction Transistors," *Bell Labs Tech. J.*, vol. 28, no. 3, pp. 435–489, 1949.

[6] W. Shockley, "A unipolar' field-effect' transistor," *Proc. IRE*, vol. 40, no. 11, pp. 1365–1376, 1952.

[7] P. K. Weimer, "The TFT a new thin-film transistor," *Proc. IRE*, vol. 50, no. 6, pp. 1462–1469, 1962.

[8] P. K. Weimer, "A p-type tellurium thin-film transistor," *Proc. IEEE*, vol. 52, no. 5, pp. 608–609, 1964.

[9] P. K. Weimer, F. V. Shallcross, and H. Borkan, "A coplanar-electrode insulated-gate thin-film transistor," *IEEE Trans. Electron Devices*, vol. 10, no. 5, pp. 335–335, 1963.

[10] B. J. Lechner, F. J. Marlowe, E. O. Nester, and J. Tults, "Liquid crystal matrix displays," *Proc. IEEE*, vol. 59, no. 11, pp. 1566–1579, 1971.

[11] P. G. Le Comber, W. E. Spear, and A. Ghaith, "Amorphous-silicon field-effect device and possible application," *Electron. Lett.*, vol. 15, no. 6, pp. 179–181, 1979.

[12] T. Moustakas, "Sputtered hydrogenated amorphous silicon," *J. Electron. Mater.*, vol. 8, no. 3, pp. 391–435, 1979.

[13] A. Madan and R. Martins, *From materials science to applications of amorphous, microcrystalline and nanocrystalline silicon and other semiconductors*. Taylor & Francis, 2009. [14] A. Juliana, S. W. Depp, B. Huth, and T. Sedgwick, "Thin-film polysilicon devices for flat-panel display circuitry," in *SID International Symposium Digest of Technical Papers*, 1982, pp. 38–39.

[15] T. Nishimura, Y. Akasaka, H. Nakata, A. Ishizu, and T. Matsumoto, "Characteristics of TFT fabricated in laser-recrystallized polysilicon for active LC display," in *PROCEEDINGS OF THE SID*, 1982, vol. 23, pp. 209–213.

[16] M. Matsui, Y. Shiraki, Y. Katayama, K. L. I. Kobayashi, A. Shintani, and E. Maruyama,

"Polycrystalline-silicon thin-film transistors on glass," *Appl. Phys. Lett.*, vol. 37, no. 10, pp. 936–937, Nov. 1980.

[17] R. De Surville, M. Jozefowicz, L. T. Yu, J. Pepichon, and R. Buvet, "Electrochemical chains using protolytic organic semiconductors," *Electrochimica Acta*, vol. 13, no. 6, pp. 1451–1458, 1968.

[18] M. Pope and C. E. Swenberg, "Electronic processes in organic molecular crystals," *Oxf. Univ. Press N. Y. Tang CW VanSlyke SA 1987 Org. Electroluminescent Diodes Appl Phys Lett*, vol. 51, no. 913, pp. 89–103, 1982.

[19] H. Hoegl, "On Photoelectric Effects in Polymers and Their Sensitization by Dopants1," *J. Phys. Chem.*, vol. 69, no. 3, pp. 755–766, Mar. 1965.

[20] H. Shirakawa, E. J. Louis, A. G. MacDiarmid, C. K. Chiang, and A. J. Heeger, "Synthesis of electrically conducting organic polymers: halogen derivatives of polyacetylene,(CH) x," *J. Chem. Soc. Chem. Commun.*, no. 16, pp. 578–580, 1977.

[21] F. Ebisawa, T. Kurokawa, and S. Nara, "Electrical properties of polyacetylene/polysiloxane interface," *J. Appl. Phys.*, vol. 54, no. 6, pp. 3255–3259, 1983.

[22] F. So, *Organic electronics: materials, processing, devices and applications*. CRC press, 2009.

[23] Graciela Nall, *Organic Electronics*. The English Press, 2011.

[24] J. J. Brondijk, Device physics of organic field-effect transistors. s.n., 2012.

[25] Klauk, Hagen, ed. Organic electronics: materials, manufacturing, and applications. John Wiley & Sons, 2006.

[26] Y. W. Kwon *et al.*, "Transparent Transistors Based on Semiconducting Oxides," *MRS Online Proc. Libr. Arch.*, vol. 786, ed 2003.

[27] Z. Galazka, "6 - Growth Measures to Achieve Bulk Single Crystals of Transparent

Semiconducting and Conducting Oxides," in *Handbook of Crystal Growth (Second Edition)*, P.

Rudolph, Ed. Boston: Elsevier, 2015, pp. 209–240.