#### الجمهورية الجزائرية الدموقراطية الشعبية République Algérienne Démocratique et Populaire وزارة التعليم العالي و البحث العلمي Ministère de l'enseignement supérieur et la recherche scientifique

Université Mohamed Khider – Biskra Faculté des Sciences et de la technologie Département :Génie électrique Ref :.....

جامعة محمد خيضر بسكرة كلية العلوم و التكنولوجيا قسم: الهندسة الكهرابانية المرجع:......

Thèse présentée en vue de l'obtention Du diplôme de

Doctorat LMD en : électronique

Spécialité (Option) : Micro-électronique

# Intitulé

(Extraction des paramètres électrique d'une diode à barrière de Schottky (SBD) à base de phosphure d'indium de type n (n-InP) par I-V-T et C-V-T)

Présentée par :

# Fritah Abdallah

Soutenue publiquement le : 03/07/2017

# Devant le jury composé de :

| Nourdine Sengouga   | Professeur              | Président     | Université de Biskra |

|---------------------|-------------------------|---------------|----------------------|

| Lakhdar Dehimi      | Professeur              | Rapporteur    | Université de Batna  |

| Achour Saadoune     | Maitre de conférences A | Co-Rapporteur | Université de Biskra |

| Khaled Bekhouche    | Maitre de conférences A | Examinateur   | Université de Biskra |

| Nacereddine Lakhdar | Maitre de conférences A | Examinateur   | Université de Eloued |

# Extraction of the electrical parameters of a Schottky barrier diode (SBD) based on n type indium phosphide (n-InP) by I-V-T and C-V-T characteristics

**Dissertation in**

**Micro-Electronics**

by

Fritah Abdallah

In Fulfilment of the Requirements for the Degree of **Doctor of Philosophy**

# **Dedication**

To my dear parents,

who supported me to complete my

study and achieve my doctoral degree.

# Acknowledgements

First of all, I want to thank my supervisor, Pr Lakhdar Dehimi, for taking me on as a student, providing challenging problems to work on and for his guidance, support and patience during this study course. As well as my co-supervisor Dr Saadoune Achour. My research would not have been accomplished without their help.

Next, I would like to thanks LMSM director Pr. Sengouga Noureddine for his help during the past years of my research in LMSM. He was very responsive every time I asked for his help.

Also, my thanks to Dr. Bekhouch Khaled for his valuable contribution and discussions in reviewing of my paper.

Furthermore. I would like to express my gratitude to the members of my dissertation committee: Pr. Sengouga noureddine, Dr. Bekhouch Khaled and Dr. Nacereddine Lakhdar for generously offering their time throughout the preparation and reviewing of this document.

I will also take this opportunity to acknowledge Pr. Bahattin Abay "professor at solid state physics department of Ataturk university" for his collaboration and for providing experimental data.

My greatest gratitude goes to my friends, because of their help i was able to overcome many obstacles during the past years in laboratory.

Finally, I would like to thank my family for their continuous support and encouragement.

#### ملخص

الوصلة معدن-نصف ناقل تعتبر بنية اساسية في مجال صناعة انصاف النواقل بحكم انها تستخدم في كثير من النبائط المهمة مثل مقحل ماسفات وموسفات لهاذا توصيف السطح بين الناقل ونصف الناقل له أهمية كبيرة. خلال العقدين الأخيرين الخاصيتين سعة-جهد وتيار-جهد هما الأكثر تقنيات التوصيف المستخدمة لدراسة الصمام الثنائي من نوع شوتكي في مجال حرارة واسع.

في هذه الاطروحة بنية شوتكي من نوع Au/n-InP/AuGe تمت دراستها عن طريق الخاصيتين سعة-جهد وتيار جهد في مجال الحرارة 400-100 كلفن وذلك عند تواجد وغياب عيوب السطح و العيوب الداخلية و تيار النفق. هذه المحاكات تمت تنفيذها ببرنامج المحاكات سيلفاكو-تيكاد وذلك بستعمال النماجذ الفزيائية المناسبة لشرح السلوك الغير طبيعي لصمام الثنائي شوتكي الملاحضة تجريبيا وهي انحراف منحنى رتشردسن من الشكل الخطي وأيضا ارتباط عامل المثالية وحاجز شوتكي المستخرج من الخاصية سعة-جهد وتيار-جهد بالحرارة وأخيرا الاختلاف بين حاجز شوتكي المستخرج من الخاصية سعة-جهد وتيار-جهد.

النتائج المتحصل عليها تعطي تفسيرا جديدا لارتباط المعاملات المذكورة سابقا بالحرارة وأيضا الاختلاف بين حاجز شوتكي المستخرج من الخاصية سعة-جهد وتيار-جهد. اضافتا الى ذلك النتائج المتحصل عليها تعطي تفسير محكم لتأثير عدم تجانس حاجز شوتكي وأيضا للنتائج الخاصة بمنحنى رشردسن ومنحنى رىشردسن المعدل باستخدام نموذج ورنر وغتلر وكذلك تأثير العيوب الداخلية على المقاومة التسلسلية وكذلك تقاطع الخاصيات تيار-جهد المقاسة في درجات حرارة مختلفة.

الخاصيتين سعة-جهد وتيار-جهد في مجال حرارة المتحصل عليهما بلمحاكات متوافقة مع المتحصل عليها تجريبيا وذلك بالأخذ بعين الاعتبار عيوب السطح والعيوب الداخلية وتيار النفق.

#### **Abstract**

Metal semiconductor (MS) rectifying junction is fundamental structure in semiconductor industry, since it used in important devices such as Metal-semiconductor and Metal-oxide-semiconductor field effect transistors (MESFET and MOSFET), thus the characterization of the MS interface have a great importance. In the last two decades current-voltage (I-V) and capacitance-voltage (C-V) characteristics are most used characterization methods to study Schottky junction in a wade temperature range.

In this thesis, Au/n-InP/AuGe Schottky structure diode was studied by the simulation of I-V and C-V characteristics in the temperature range 400-100 K in absence and presence of interface states, traps and tunneling current. The simulation was performed with Atlas-Silvaco-Tcad device simulator using the appropriate physical models to explain the experimentally observed abnormal behaviors of Schottky diodes which are, the deviation of Richardson plot from linearity, the temperature dependence of the zero-bias barrier height  $(\emptyset_{b0})$ , capacitance barrier height  $(\emptyset_{CV})$  and the ideality factor (n), also the discrepancy obtained between  $\emptyset_{b0}$  and  $\emptyset_{CV}$ .

Our results give new explanation to the temperature dependence of the mentioned parameters and the discrepancy obtained between  $\emptyset_{b0}$  and  $\emptyset_{CV}$ . Moreover the obtained results lead to a coherent explanation of the barrier height inhomogeneity effect, Richardson plot, modified Richardson plot with Werner and Guttler model and modified Richardson plot with Tung model. Also the effect of deep trap on the series resistance and the intersection of I-V curves measured at different temperature were explained.

Good agreement between the simulated I-V-T and C-V-T results and existing experimental data were obtained by considering interface stats, traps and tunneling current.

#### Résumé

La jonction métal-semiconducteur utiliser comme redresseur est une structure fondamentale dans l'industrie des semiconducteurs, puisqu'elle est utilisée dans des importants dispositifs comme les transistors à effet de champ (MESFET et MOSFET), pour sa la caractérisation de l'interface MS possède une grande importance. Au cours des deux dernières décennies, les caractéristiques courant- tension (I-V) et capacitance-tension (C-V) sont les méthodes de caractérisation les plus utilisées pour étudier la jonction de Schottky dans une plage de température.

Dans cette thèse, la structure de la diode Schottky Au/n-InP/AuGe a été étudié par la simulation des caractéristiques I-V et C-V dans la gamme de température 400-100 K en absence et en présence des états d'interface, pièges et le courant tunnel. La simulation a été effectuée avec le simulateur Atlas-Silvaco-Tcad en utilisant les modèles physiques appropriés pour expliquer les comportements anormaux observés expérimentalement dans les diodes Schottky qui sont la déviation de la courbe linéarité de Richardson, la dépendance de la barrière Schottky  $(\emptyset_{b0})$ , la barrière extrait à partir de la caractéristique C-V  $(\emptyset_{CV})$  et le facteur d'idéalité (n) de la température et aussi l'écart obtenu entre  $\emptyset_{b0}$  et  $\emptyset_{CV}$ .

Nos résultats donnent une nouvelle explication à la dépendance des paramètres mentionnés de la température. En plus, les résultats obtenus conduisent à une explication cohérente de l'effet d'inhomogénéité de la hauteur de barrièr, la courbe de Richardson, et la courbe modifié de Richardson avec le model de Werner et Guttler et la courbe modifié de Richardson avec le model de Tung. En outre notre résultats donne une bonne explication de l'effet des pièges profonds sur la résistance série et l'intersection des courbes I-V mesurées à différentes températures.

Un bon accord à été obtenu entre les caractéristiques I-V-T et C-V-T par simulation et mesurées en prenant en considération les états d'interface, les défauts et le courant tunnel.

# **Contents**

# page

| Dedication                                          |     |

|-----------------------------------------------------|-----|

| Acknowledgments                                     | II  |

| ملخص                                                |     |

| Abstract                                            | IV  |

| Résumé                                              | V   |

| Table of contents.                                  | VI  |

| List of figures                                     | X   |

| List of tables                                      | XIV |

|                                                     |     |

| Introduction                                        |     |

| 1.1                                                 |     |

| Introduction                                        | 1   |

| 1.2 Thesis                                          |     |

| outline                                             | 3   |

| Chapter1: Schottky barrier diode and InP properties |     |

| 1.1 Schottky                                        |     |

| contact.                                            | 4   |

| 1.1.1 Schottky barrier formation                    | 4   |

| a. Mott Schottky model                              | 4   |

| I. N-type semiconductor with $\Phi_S > \Phi_M$      | 5   |

| II. P-type semiconductor with $\Phi_S < \Phi_M$     | 6   |

| b. Fixed-separation models                          | 7   |

| c. Metal induced gap states mod                     | 9   |

| d. Bond polarization model                          | 10  |

| 1.1.2 Depletion region                             | 12 |

|----------------------------------------------------|----|

| 1.1.3 Capacitance.                                 | 14 |

| 1.1.4 Schottky effect                              | 14 |

| 1.1.5 Carrier transport mechanism                  | 16 |

| a. Thermionic emission.                            | 17 |

| b. Tunneling                                       | 19 |

| I. forward bias                                    | 20 |

| II. reverse bias:                                  | 21 |

| 1.1.6 barrier inhomogeneities                      | 21 |

| a. Werner model                                    | 22 |

| b. Tung model                                      | 25 |

| 1.2. Material property of indium phusphyde         | 30 |

| 1.2.1 Cristal                                      |    |

| structure                                          | 30 |

| 1.2.2 Energy band structure                        | 31 |

| 1.2.3 Electrical properties.                       | 31 |

| 1.2.4                                              |    |

| Doping                                             | 32 |

| 1.2.5 Interface                                    | 33 |

| Chapter 2: physical models and simulation software |    |

| 2.1. Physical models used in simulation.           | 34 |

| 2.1.1. Density of stats.                           | 34 |

| 2.1.2. Band gap                                    | 34 |

| 2.1.3. Low field mobility                          | 35 |

| 2.1.4. Shockley-Read-Hall.                         | 35 |

| 2.1.5. Auger recombination                         | 35 |

| 2.1.6. Impact ionization                           | 36 |

| 2.1.7. Incomplete ionization of impurities         | 36 |

| 2.1.8. Thermionic emission.                        | 36 |

| 2.1.9. Universal Schottky tunneling                | 37 |

| 2.1.10. Image force lowering.                      | 37 |

| 2.2 The simulation software                        | 37 |

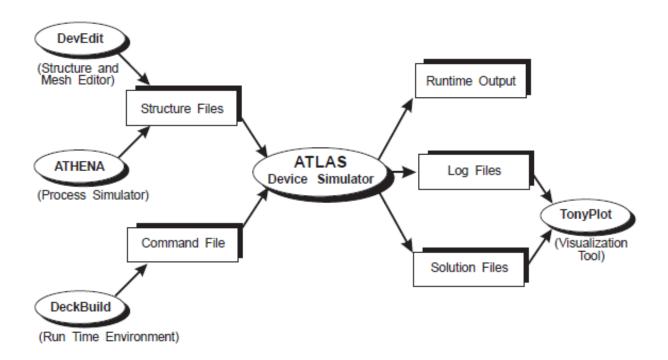

| 2.2.1. Atlas inputs and outputs                               | 38  |

|---------------------------------------------------------------|-----|

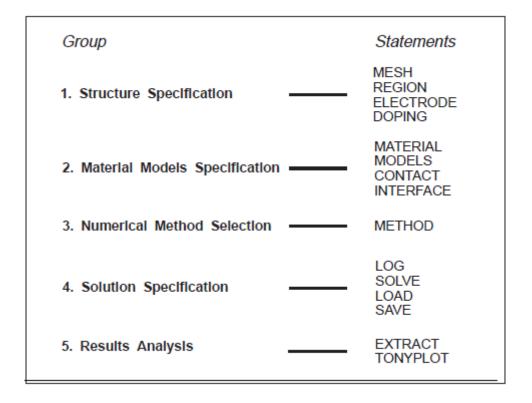

| 2.2.2 The Atlas commands                                      | 39  |

| a. Structure specification                                    | 40  |

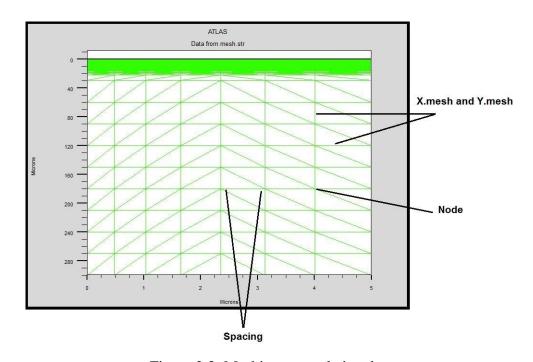

| I. Specifying the initial mesh                                | 40  |

| II. Region                                                    | 42  |

| III. Electrode                                                | 42  |

| IV. Doping                                                    | 43  |

| b. Material and model specification                           | 43  |

| I. Specifying material properties                             | 43  |

| II. Specifying Physical Models                                | 44  |

| III. Specifying Contact Characteristics                       | 45  |

| IV. Specifying Interface Properties                           | 45  |

| c. Numerical method                                           |     |

| selection                                                     | 46  |

| d. Solution specification.                                    | 46  |

| e. Results Analysis                                           | 47  |

| I. Tony plot                                                  | 47  |

| II. Extract                                                   | 47  |

| Chapter 3: Extraction methods of Schottky diode parameter     | ers |

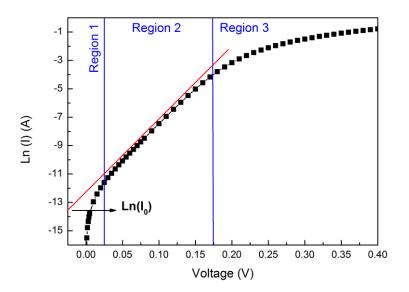

| 3.1. Current-voltage methods                                  | 49  |

| 3.1.1. Standard method                                        | 49  |

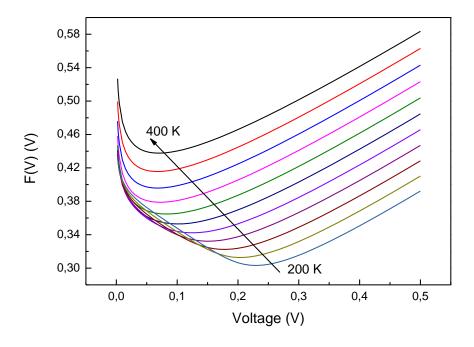

| 3.1.2. Norde method.                                          |     |

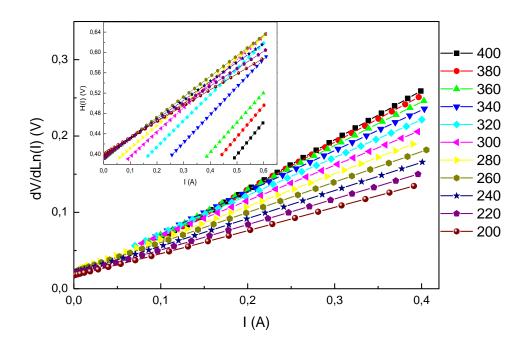

| 3.1.3. Cheung method                                          | 52  |

| 3.2. Flat-band barrier height                                 |     |

| 3.3. Capacitance voltage method                               |     |

| 3.4. Activation energy measurement                            | 54  |

| 3.4.1. Modified Richardson plot with Werner and Guttler model |     |

| 3.4.2. Modified Richardson plot with Tung model               | 57  |

| Chapter 4: Results and discussion                             |     |

| 4.1. Analyzing of experimental results                        | 59  |

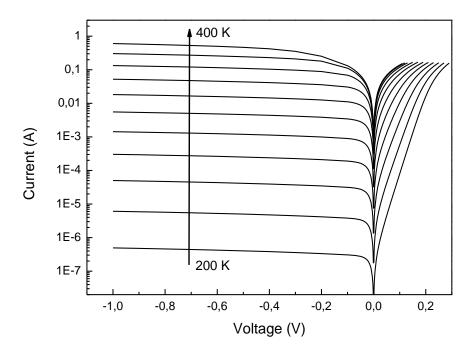

| 4.2. High temperatures I-V characteristics.                   | 60  |

| 4.2.1. Near Ideal diode                                       | 60  |

| a. Choosing the work function value                                    | 61    |

|------------------------------------------------------------------------|-------|

| b. Temperature effect.                                                 | 62    |

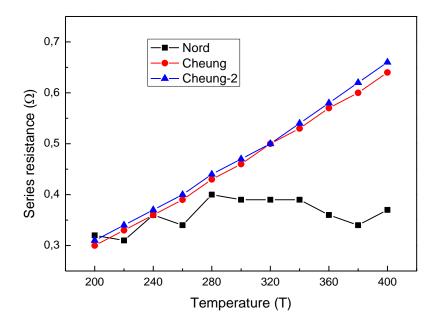

| c. Parameters extraction.                                              | 62    |

| 4.2.2. Real diode.                                                     | 65    |

| a. Native oxide                                                        | 66    |

| b. I-V-T characteristics.                                              | 67    |

| c. Parameters extraction.                                              | 69    |

| d. Richardson plot                                                     | 72    |

| 4.3. Low temperature I-V-T characteristics                             | 73    |

| 4.3.1. Modified Richardson plot with Tung model                        | 74    |

| 4.3.2. I-V-T characteristics.                                          | 76    |

| 4.3.4. Parameters extraction.                                          | 81    |

| 4.3. C-V-T characteristics.                                            | 84    |

| 4.3.1 Near ideal diode                                                 | 84    |

| a. Temperature effect                                                  | 84    |

| b. Barrier height extraction                                           | 85    |

| 4.3.2. Real diode                                                      | 86    |

| a. Native oxide effect                                                 | 86    |

| b. C-V-T characteristics.                                              | 87    |

| c. Barrier height extraction                                           | 89    |

| 4.4. The discrepancy between the barrier height extracted from C-V and | . I-V |

| characteristics                                                        | 90    |

| 4.5. Neutral region trap effect on the series resistance               | 91    |

| 4.6. I-V-T characteristics intersection.                               | 93    |

| Conclusion                                                             | 95    |

| References                                                             | 97    |

| Publication                                                            | 105   |

|                                                                        |       |

# List of figures

| Figure 1.1: Energy band diagram of a Metal and semiconductor before contact5                              |

|-----------------------------------------------------------------------------------------------------------|

| Figure 1.2: Energy band diagram of an ideal Metal-n-type semiconductor in thermal                         |

| Equilibrium5                                                                                              |

| Figure 1.3: Energy band diagram of an ideal Metal-n-type: (a) in forward bias, (b) in reverse             |

| bias6                                                                                                     |

| Figure 1.4: Energy band diagram of an ideal Metal-p-type semiconductor in thermal                         |

| equilibrium7                                                                                              |

| Figure 1.5: Energy band diagram of Metal-n-type semiconductor based on Cowley and Sze                     |

| Model8                                                                                                    |

| Figure 1.6: Schematic representation of the wave function at metal-semiconductor                          |

| interface illustrating MIGS concept9                                                                      |

| Figure 1.7: Band diagram of the negative charge model, incorporating the effect of the                    |

| exponential decay of a density of MIGS10                                                                  |

| Fig.1.8: A cross-sectional view of the model of a metal semiconductor interface used in the               |

| bond polarization theory                                                                                  |

| Figure 2.9: (a) Energy band diagram, (b) electric field, (c) potential distribution, and (b) space-charge |

| distribution for a metal/n-type semiconductor Schottky barrier diode                                      |

| Figure 1.10: The induce image charge inside the metal of Schottky effect                                  |

| Figure 1.11: Energy band diagram showing Schottky effect at: (a) metal-vacuum interface in                |

| the presence of an applied electric field (b) metal-semiconductor interface under different               |

| biasing condition                                                                                         |

| Figure 1.12: The basic transport mechanisms at metal-semiconductor junction                               |

| Figure 1.13: Field and thermionic-field emission under forward bias                                       |

| Figure 1.14: Two-dimensional band diagram of an inhomogeneous Schottky contact22                          |

| Figure 1.15: Plot of differences between Schottky barriers for two PtSi/Si diodes Curves (a)              |

| and (c) show the difference between values as derived from the conventional                               |

| evaluation of I/U and C/U data. Curves (b) and (d) follow from curves (a) and (c)                         |

| after correcting the capacitance barrier for the bias dependence of the mean                              |

| Schottky barrier according to Equation 2.57                                                               |

| Figure 1.16: The temperature-dependent ideality data of our PtSi/Si diodes follow Equation                |

| 2.56                                                                                                      |

| Figure 1.17: Geometries and coordinates of examples of the inhomogeneities in Tung model.                 |

| (a) Circular patch, (b) narrow strip.                                                                 | 26   |

|-------------------------------------------------------------------------------------------------------|------|

| Figure 1.18: CBM potentials along the z axis in close to a low-SBH patch, illustrating the            |      |

| influence of the radius of a low-SBH patch on potential pinch-off                                     | 27   |

| Figure 1.19: Typical current-voltage response of an ideal and inhomogeneous diode                     | 29   |

| Figure 1.20: Zinc-blende structure for Indium Phosphide                                               | 30   |

| Figure 1.21: Energy band gap structure of InP at 300 K.                                               | 31   |

| Figure 2.1: Atlas inputs and outputs.                                                                 | 39   |

| Figure 2.2: Atlas command with the primary statements in each group.                                  | 40   |

| Figure 2.3: Meshing example in atlas.                                                                 | 41   |

| Figure 3.1: Typical I-V characteristic of Schottky diode.                                             | 50   |

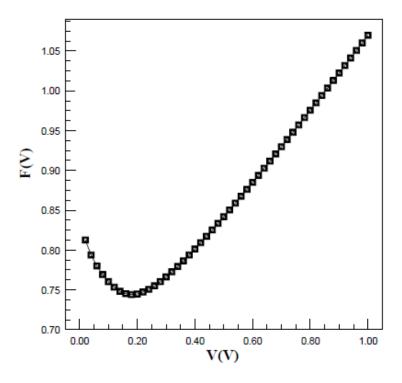

| Figure 3.2: Example of F(V) vs. V plot from                                                           | 51   |

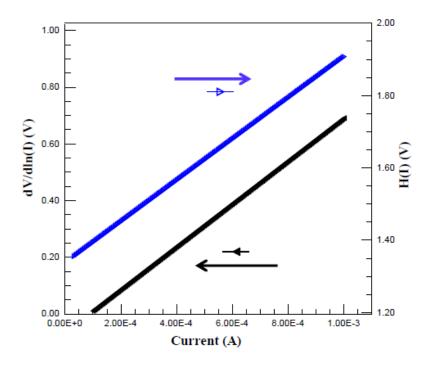

| Figure 3.3: Example of $dV/d(lnI)$ vs. $I$ and $H(I)$ vs. $I$ plots from                              | 52   |

| Figure 3.4: 1/C <sup>2</sup> -V plot for two Al/n-GaAs two Schottky diodes deposited By two different | ıt   |

| methods                                                                                               | 54   |

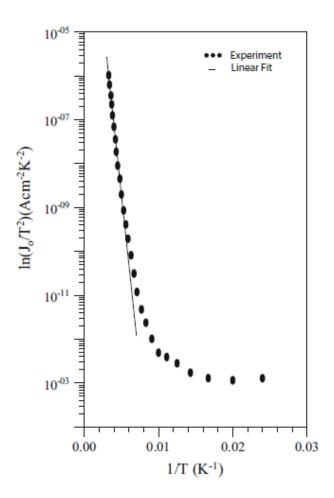

| Figure 3.5: Example of Richardson plot from.                                                          | 55   |

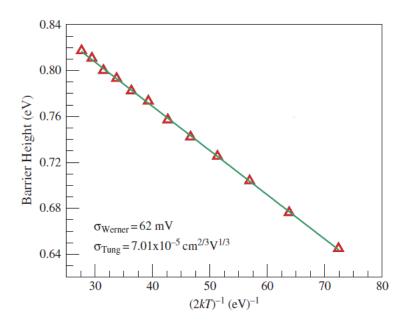

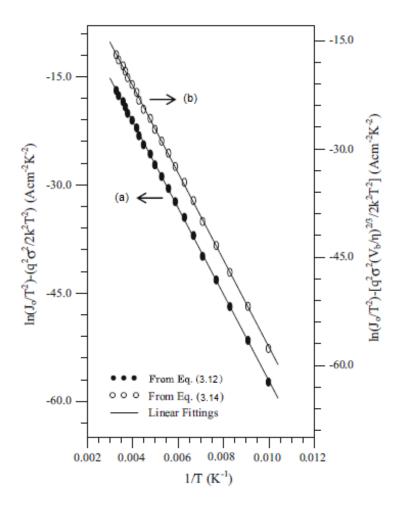

| Figure 3.6: Example of $\emptyset_{b0}$ vs. 1/2kT plot from.                                          | 56   |

| Figure 3.7: Example of modified Richardson plot with: (a) Werner and Cutller model, (b)               |      |

| Tung model                                                                                            | 58   |

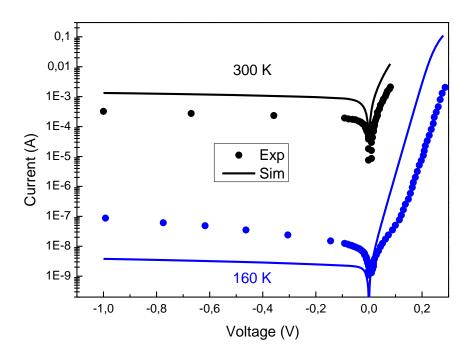

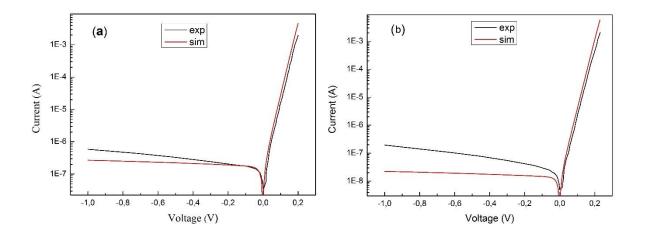

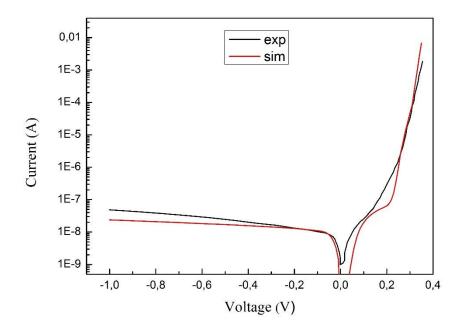

| Figure 4.1: The experimental and simulated current voltage characteristic at 300 and                  |      |

| 160 K                                                                                                 | 59   |

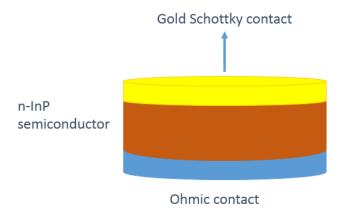

| Figure 4.2: The structure of the near ideal diode                                                     | 60   |

| Figure 4.3: The simulated current voltage characteristic at 300 K of the ideal diode for differ       | rent |

| work function                                                                                         | 61   |

| Figure 4.4: The simulated semi-logarithmic current-voltage characteristics of the ideal dio-          | de   |

| at various temperature range                                                                          | 62   |

| Figure 4.5: The plot of dV/d(LnI) versus I (insert figure: plot of H(I) versus I) of the near         |      |

| ideal diode in the temperature range 200-400 K                                                        | 64   |

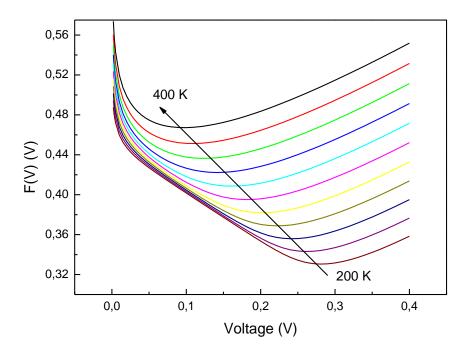

| Figure 4.6: The F(V) versus V plot of the near ideal diode in the temperature range                   |      |

| 200- 400                                                                                              | 64   |

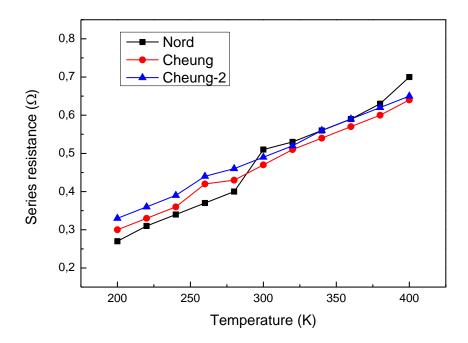

| Fig.4.7: The series resistance of the near ideal diode calculated with various methods in the         |      |

| temperature range 200-400 K                                                                           |      |

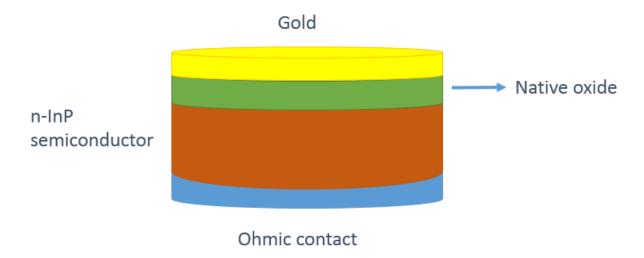

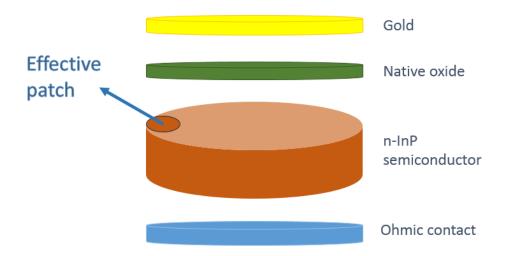

| Figure 4.8: the structure of the real diode                                                           | 66   |

| Figure 4.9: Native exide layer effect on current transport process                                    | 66   |

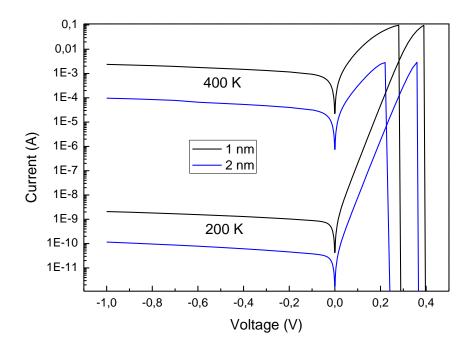

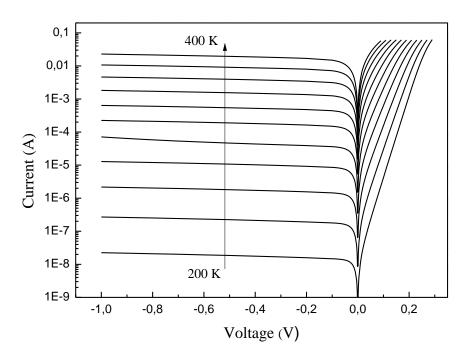

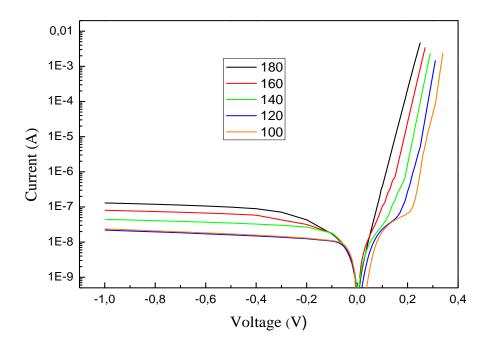

| Figure 4.10: The Simulated semi-logarithmic current voltage characteristic of the real diode at         |

|---------------------------------------------------------------------------------------------------------|

| various temperature range                                                                               |

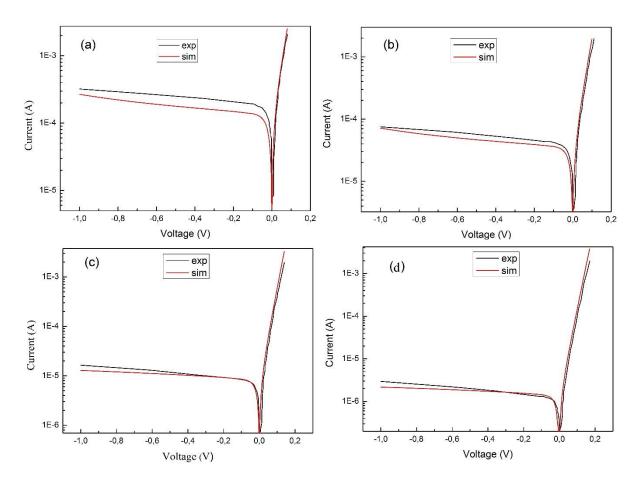

| Figure 4.11: Comparison of the simulated I-V characteristics with measurement at:                       |

| (a) 300 K, (b) 280 K, (c) 260, (d) 24068                                                                |

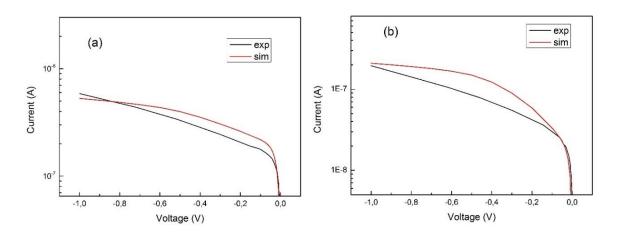

| Figure 4.12: Comparison of the simulated I-V characteristics with measurement at:                       |

| (a) 220 K, (b) 200 K69                                                                                  |

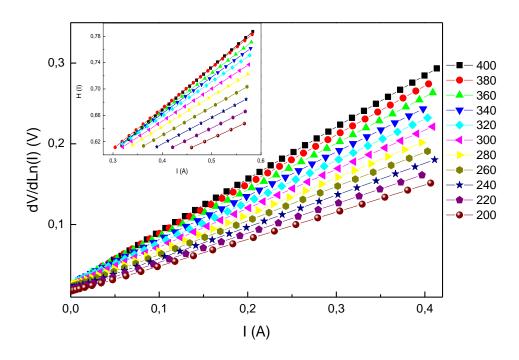

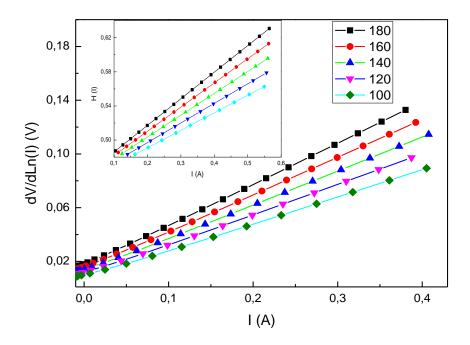

| Figure 4.13: The plot of dV/d(LnI) versus I (insert figure: plot of H(I) versus I) of the real          |

| diode in the temperature range 200-400 K71                                                              |

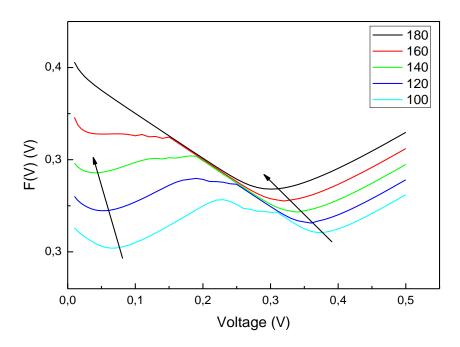

| Figure 4.14: The F(V) versus V plot of the real diode in the temperature range 200-40071                |

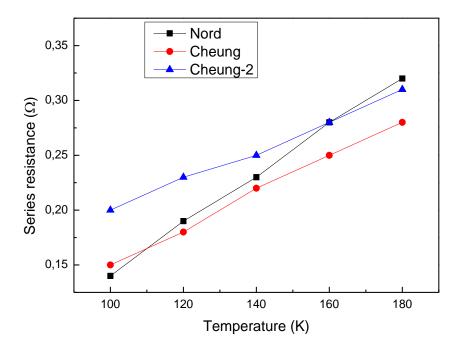

| Figure 4.15: The series resistance of the real diode calculated with various methods in the temperature |

| range 200-400 K                                                                                         |

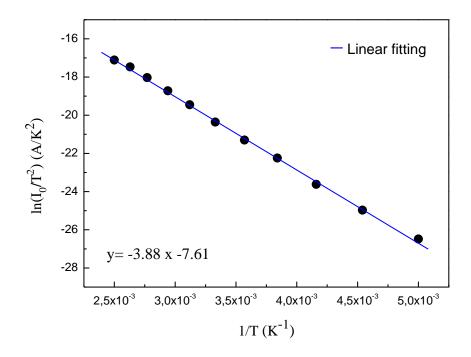

| Figure 4.16: Richardson plot of $ln(I_0/T^2)$ versus $1/T$ of the real diode                            |

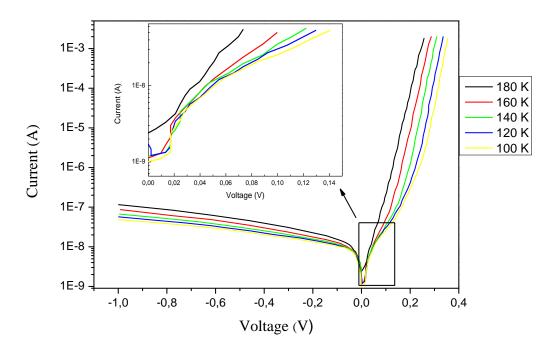

| Figure 4.17 The experimental low temperature I-V characteristics (the insert show zoom-in on            |

| the effective patch bias region)74                                                                      |

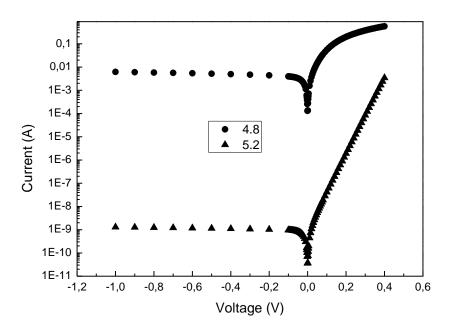

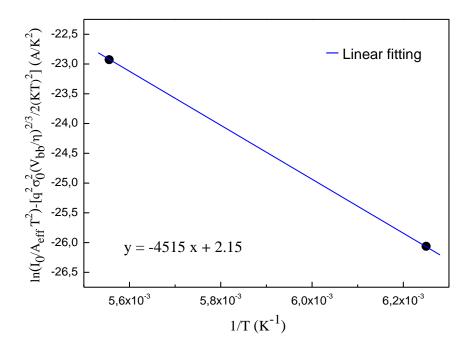

| Figure 4.18: Modified Richardson plot with Tung model                                                   |

| Figure 4.19: The structure of the inhomogeneous diode                                                   |

| Figure 4.20: The simulated low temperature I-V characteristics with inhomogeneous SBD78                 |

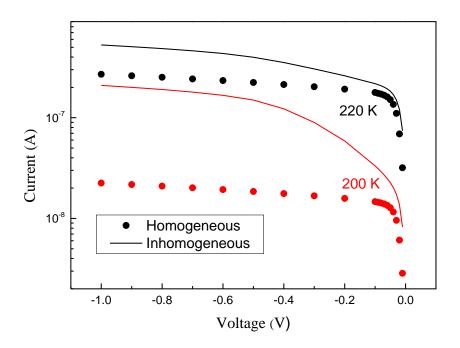

| Figure 4.21: The simulated reverse current in 220 and 200 K with homogeneous and                        |

| inhomogeneous SBD                                                                                       |

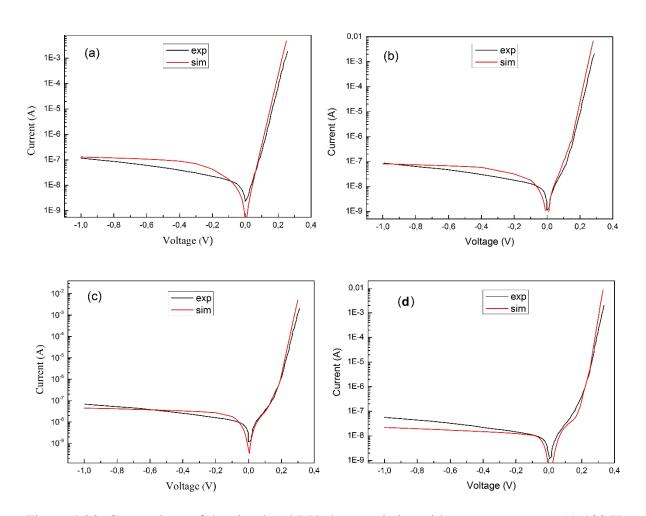

| Figure 4.22: Comparison of the simulated I-V characteristics with measurement at:                       |

| (a) 220 K, (b) 200 K80                                                                                  |

| Figure 4.23: Comparison of the simulated I-V characteristics with measurement at:                       |

| (a) 180 K, (b) 160 K, (c) 140, (d) 120 K80                                                              |

| Figure 4.24: Comparison of the simulated I-V characteristics with measurement at 100 K81                |

| Figure 4.25: The plot of $dV/d(LnI)$ versus I (insert figure: plot of $H(I)$ versus I) of the real      |

| diode in the temperature range 180-100 K                                                                |

| Figure 4.26: The $F(V)$ versus $V$ plot of the real diode in the temperature range $180\text{-}10083$   |

| Figure 4.27: The series resistance of the real diode calculated with various methods in the             |

| temperature range 180-100 K83                                                                           |

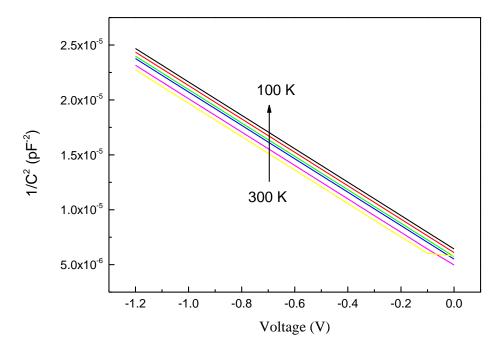

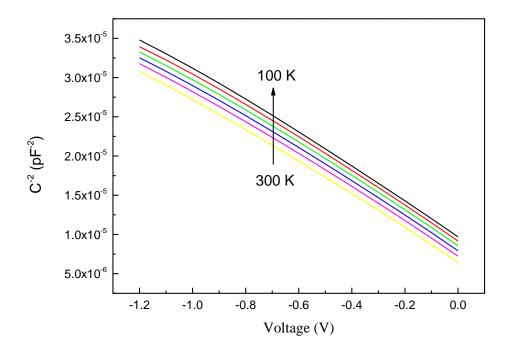

| Figure 4.28: The simulated $1/C^2$ -V characteristics of the near ideal diode in the temperature        |

| range 300-100 K84                                                                                       |

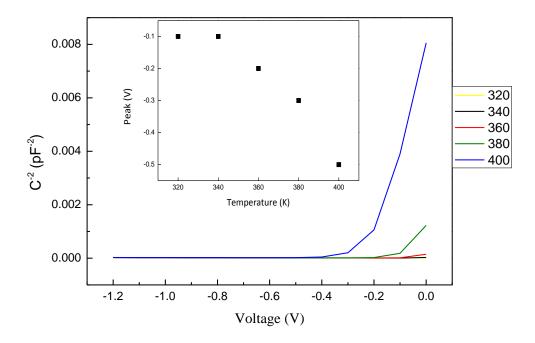

| Figure 4.29: The simulated $1/C^2$ -V characteristics of the near ideal diode in the temperature        |

| range 400-320 K                                                                                  | 85 |

|--------------------------------------------------------------------------------------------------|----|

| Figure 4.30: Effect of native oxide on the capacitance at high temperature                       | 87 |

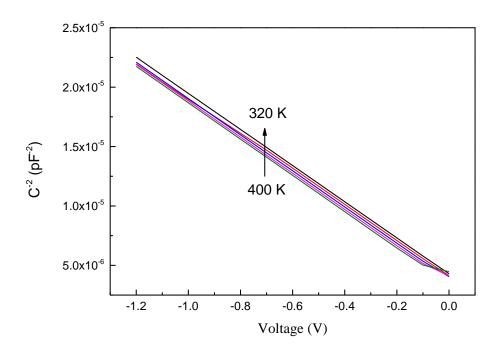

| Figure 4.31: The simulated $1/C^2$ -V characteristics of the real diode in the temperature range | ;e |

| 300-100 K                                                                                        | 88 |

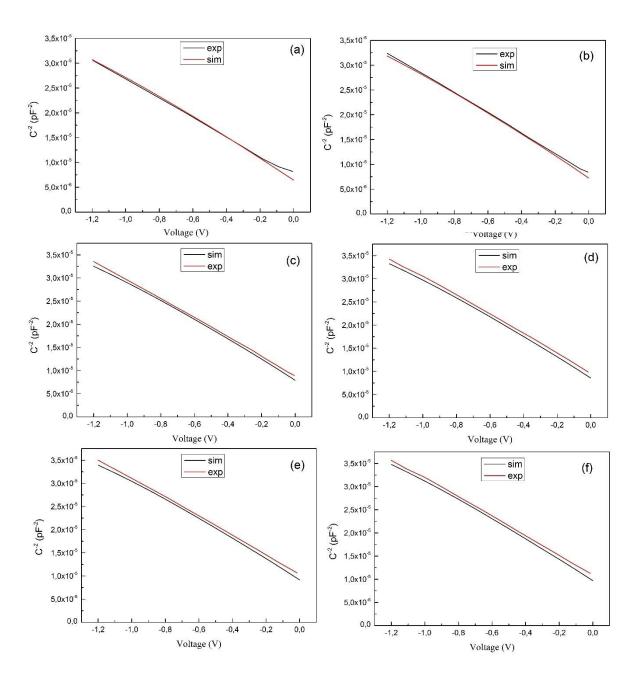

| Figure 4.32: Comparison of the simulated C-V characteristics with measurement at:                |    |

| (a) 300 K, (b) 260 K, (c) 220, (d) 180, (e) 140, (f) 100 K                                       | 89 |

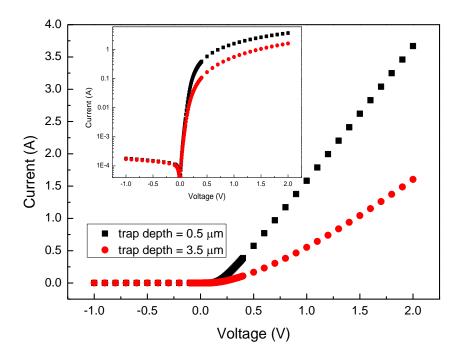

| Figure 4.33: The I-V characteristic of the real diode with different trap depth at 300 K in      |    |

| linear scale (the insert in semi-logarithmic scale)                                              | 92 |

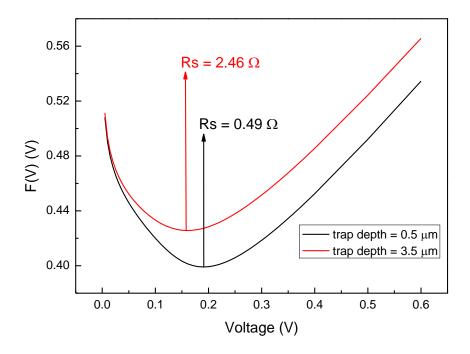

| Figure 4.34: The F(V) versus V plot of the I-V characteristic in Figure 4.27                     | 92 |

| Figure 4.35: The I-V characteristic of the real diode at 300 and 200 K with series resistance    | e  |

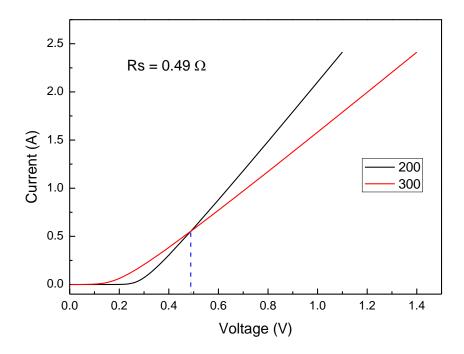

| values equal to $0.49~\Omega$                                                                    | 94 |

| Figure 4.36: The I-V characteristic of the real diode at 300 and 200 K with series resistance    | e  |

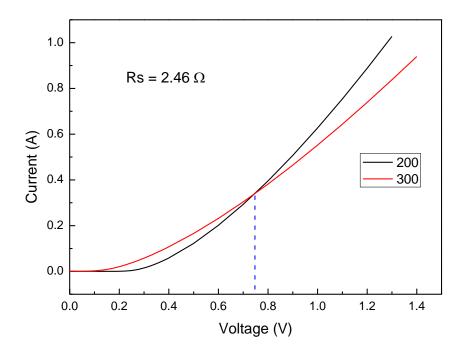

| values equal to 2.46 $\Omega$                                                                    | 94 |

# List of tables

| Table 1.1: Parameters for electron transport at an inhomogeneous SB with one-half of a               | ì    |

|------------------------------------------------------------------------------------------------------|------|

| Gaussian distribution.                                                                               | 28   |

| Table 1.2: Important parameters of InP at 300 K.                                                     | 32   |

| Table 2.1 The parameters of material statement used in the simulation                                | 44   |

| Table 4.1: The extracted n and $\emptyset_{b0}$ values of the near ideal diode with different method | s in |

| temperature range 200-400 K.                                                                         | 63   |

| Table 4.2: The extracted n and $\emptyset_{b0}$ values of the real diode with different methods in   |      |

| temperature range 200-400 K.                                                                         | 70   |

| Table 4.3: Effective patch parameters used in modified Richardson plot                               | 75   |

| Table 4.4: The effective patch barrier and area used to regenerate the low temperature               |      |

| experimental I-V characteristics                                                                     | 77   |

| Table 4.5: The extracted n and $\emptyset_{b0}$ values of the real diode with different methods in   |      |

| temperature range 180-100 K                                                                          | 82   |

| Table 4.6: The simulated $\Phi_{CV}$ values of the near real diode                                   | 86   |

| Table 4.7: The simulated $\Phi_{CV}$ values of the real diode with experimental ones                 | 90   |

## Chapter 1

# Schottky barrier diode and InP properties

#### 1.1 Schottky contacts

#### 1.1.1 Schottky barrier formation

The first-order theory of the formation of a Schottky barrier (SB) is the view attributed to Walter Schottky himself originally, and also to Neville Mott in 1939. The Schottky-Mott theory is often violated at a real MS interface since it does not place any emphasis on the MS interface properties. To explain the observed departure of the experimentally obtained SBH from Schottky-Mott relationship, several models was developed based on the concept of Fermi-level pinning (FLP). All this model (gap state models) suggest the presence of an interface specific region (ISR) and surface states in the band gap of the semiconductor named gap states (GS). The gap state models can be divided into two groups, based on whether the metal and the semiconductor are assumed to interact or not [31].

#### a. Mott-Schottky model

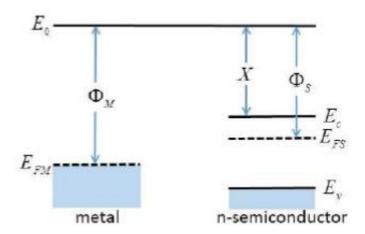

The model proposes that the SBH between a metal and a semiconductor depend only on the work function of the metal  $q\Phi_M$  and the electron affinity of the semiconductor  $q\chi_S$ . as shown in Figure (1.1), the work function is the energy difference between the vacuum level and the Fermi level (the minimum kinetic energy required for an electron to escape from the metal surface in to free space at T=0~K), where electron affinity is the energy difference between the vacuum and the bottom of the conduction band  $E_C$ .

When the metal and the semiconductor are in separate systems the vacuum level is aligned in both materials. After the two materials contacted, electrons flow from the higher to the lower energy level and thermal equilibrium established as a single system. The Fermi levels on both sides will line up leading the creation of a depletion (Schottky case) or accumulation region

(ohmic case) in the semiconductor, depending on the type of the semiconductor and the value of its affinity.

Figure 1.1: Energy band diagram of a Metal and semiconductor before contact.

#### I. N-type semiconductor with $\Phi_S > \Phi_M$ :

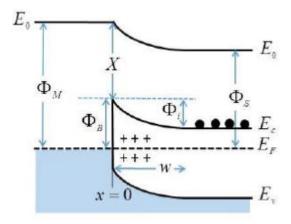

After the alignment of the Fermi-levels a depletion layer will created in the semiconductor with the ionized donor  $N_{d^+}$  and an accumulation of electrons at the interface of the metal, in which the number of positive charge in the semiconductor is equal to the negative charge at the interface of the metal. The difference between the conduction band and the Fermi-level decrease from the interface to the bulk of the semiconductor, due to the electrical field of the created space charge. The vacuum level moves in the same manner of the conduction band to keep the affinity value constant.

Figure 1.2: Energy band diagram of an ideal Metal-n-type semiconductor in thermal equilibrium.

The energy barrier height at the metal/semiconductor interface shown in Figure 1.2, is the energy needed by electrons to can move from the semiconductor to the metal after thermal equilibrium and is given by:

$$q \Phi_{Bn0} = q \left( \Phi_m - \chi_{\varsigma} \right) \tag{1.1}$$

If we apply a positive voltage to the semiconductor with respect to the metal (reverse bias), the semiconductor-to-metal barrier height increases. While  $\Phi_{Bn0}$  remains constant in this idealized case. If a positive voltage is applied to the metal with respect to the semiconductor (forward bias), the semiconductor-to-metal barrier  $V_{bi}$  (built-in voltage) is reduced while  $\Phi_{Bn0}$  again remains essentially constant. In this situation, electrons can more easily flow from the semiconductor into the metal since the barrier has been reduced.

The energy-band diagrams for the reverse and forward bias are shown in Figure 1.3.

Figure 1.3: Energy band diagram of an ideal Metal-n-type semiconductor: (a), in forward bias (b) in reverse bias.

#### II. P-type semiconductor with $\Phi_S < \Phi_M$ :

After the alignment of the Fermi-levels a depletion layer will created in the semiconductor with the ionized acceptor  $N_a$ - and a deficit of electrons at the interface of the metal. The difference between the conduction band and the Fermi-level increase from the interface to the bulk of the semiconductor, due to the electrical field of the created space charge. The vacuum level moves in the same manner of the conduction band to keep the affinity value constant.

Figure 1.4: Energy band diagram of an ideal Metal-p-type semiconductor in thermal equilibrium.

The energy barrier height at the metal/semiconductor interface (Figure 1.4), is the energy needed to holes can move from the semiconductor to the metal (or equivalently, of electrons from the metal to the semiconductor) after thermal equilibrium and is given by:

$$q \Phi_{Bp0} = E_g - q \left( \Phi_m - \chi_S \right) \tag{1.2}$$

Under polarization the behavior of a p-type Schottky diode is the same as n-type Schottky diode, if we replace electrons by holes and  $\Phi_{Bn0}$  by  $\Phi_{Bp0}$  [32-34].

#### **b.** Fixed-separation models:

The fixed-separation models (separation view of interface states) with the Mott-Schottky model discussed above, comprise the group of non-interacting SBH models. This assumption based on the absence of charge rearrangement at MS interface, in other word it does not give the real overall dipole of the MIS system.

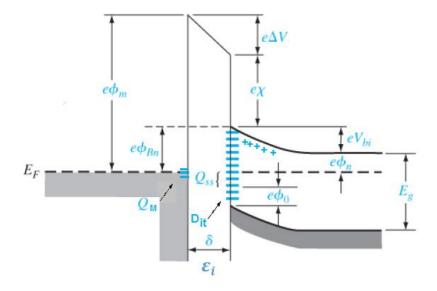

The first model was proposed by Bardeen in 1947 [35] suggesting the surface states localized at the surface of the semiconductor to be the source of the FLP. The barrier in this model depend only to the surface states and is independent to the metal work function. Later in 1965 Cowley and Sze [36] developed a more realistic model, which take into account the effect of both surface states, the metal work function on the SBH and the interface dipole.

Cowley and Sze was derived based on the following assumptions: (1) the contact between the metal and the semiconductor has an interfacial layer of the order of atomic dimensions; it is further assumed that this layer is transparent to electrons with energy greater than the potential barrier but can withstand potential across it. (2) The surface state density (per unit area per

electron volt) at the interface is a property only of the semiconductor surface and is independent of the metal. The schematic shown in Figure 1.5 is the energy band diagram illustrating model.

Figure 1.5: Energy band diagram of Metal-n-type semiconductor based on Cowley and Sze model [36].

Where  $\emptyset_m$  is the work function of metal,  $\emptyset_{Bn}$  is the barrier height without image force lowering,  $\emptyset_0$  is the neutral level of interface states,  $\Delta$  is the potential across interfacial layer,  $\chi$  is the electron affinity of semiconductor,  $V_{bi}$  is the built-in potential,  $\delta$  is the interfacial layer thickness,  $\varrho_{sc}$  space charge density in semiconductor,  $\varrho_{ss}$  interface trap charge,  $\varrho_{M}$  surface charge density on metal,  $D_{it}$  interface trap density and  $\varepsilon_{i}$  is the interface layer permittivity.

With the above assumptions, the barrier height for n-type semiconductor-metal contacts is found to be a linear combination of the metal work function  $\Phi_M$  and a quantity  $\Phi_0$ , which is defined as the energy below which the surface states must be filled for charge neutrality at the semiconductor surface. For constant surface state density the theoretical expression obtained is

$$\Phi_{Bn0} = y \left( \Phi_m - \chi_{\varsigma} \right) + (1 - y) \left( E_g - \Phi_0 \right) - \Delta \Phi_{Bn}$$

(1.3)

Where y is equivalent to the interface behavior parameter  $S = (\frac{d\Phi_{Bn0}}{d\Phi_{m}})$ .

$$y = \left(\frac{\varepsilon_i}{\varepsilon_i - q^2 \delta D_{it}}\right) \tag{1.4}$$

For a high density of states  $(y \ll 1)$ , the second term on the right hand side of equation (1.3) dominates and the Fermi-level will pinned by interface states close to the level  $\Phi_0$ . In the case

where interface states are neglected,  $(y \approx 1)$  and SBH equation is identical to Mott-Schottky equation (ideal diode).

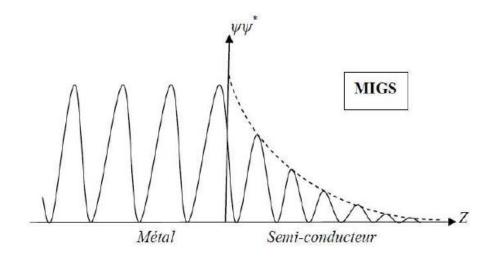

#### c. Metal induced gap states model

Metal induced gap states (MIGS) is the first interactive model developed by V. Heine in 1965 [37], he started from assumption that vacuum cleaved surface cannot contain a high density interface states which can pin the Fermi level. The interaction between the metal and semiconductor was expressed by the overlap of wave function at a MS interface, this overlap of wave function alter the electronic structure and the charge distribution in the ISR and induce electronic states in the band gap of the semiconductor.

Figure 1.6: Schematic representation of the wave function at metal-semiconductor interface illustrating MIGS concept.

Later in 1977 Louie et al [38] proved the concept theoretically for Al/(Si, GaAS, ZnSe, ZnS) interfaces and gave the MIGS denomination, then the phenomenon has been observed by First et al in 1989 [39] using scanning tunneling microscopy (STM) for Fe/GaAS (110) interface. The band banding is a kind like Figure 1.7.

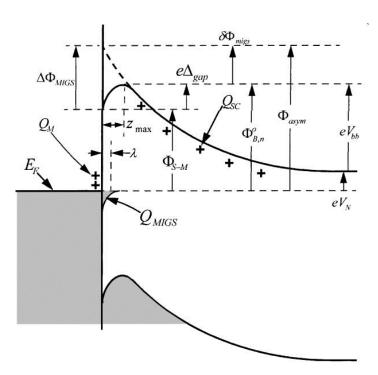

Figure 1.7: Band diagram of the negative charge model, incorporating the effect of the exponential decay of a density of MIGS.

Where  $Q_{MIGS}$  is the areal density of the net charge occupied by MGIS,  $\lambda$  is the penetration depth of MIGS into the semiconductor, and  $\delta\Phi_{MIGS}$  is the SBH lowering due to MIGS. The effective SBH, which actually controls the electronic transport, is [31]

$$\Phi_{Bn0} = (\Phi_{S-M} + \Delta \Phi_{MIGS}) - \delta \Phi_{MIGS}$$

(1.5)

Where

$$\Delta\Phi_{MIGS} \approx -\frac{e\lambda Q_{MIGS}}{\varepsilon_S} \tag{1.6}$$

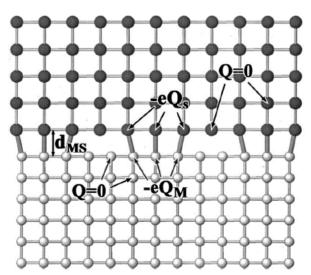

#### d. Bond polarization model:

Another interactive approach has been recently developed 2001 by Tung, which is based on the chemical interaction between the metal and semiconductor right at the interface [40]. The model is called Bond polarization theory (BPT). The theory assumes that the charge rearrangement is mostly dependent on the formation of surface bonds, and the Schottky dipole is thought to arise from the polarization of these. In order to calculate this dipole, he applied the electrochemical potential equalization (ECPE) method, which originally is a numerical method for estimating the dipole moment (the measure of the polarity of a chemical bond) of a molecule, and

considered the whole interface to be a gigantic molecule. By using this approach, he was able to calculate the transfer of charge between the atoms, and thus the dipole. The SBH is predicted to be

$$\Phi_B = y_B \left( \Phi_m - \chi_S \right) + (1 - y_B) \frac{E_g}{2}$$

(1.7)

$$y_B = 1 - \frac{e^2 d_{MS} N_B}{\varepsilon_{it} (E_g + \kappa)} \tag{1.8}$$

Where  $y_B$  is a parameter indicate the interface behaviour,  $N_B$  is the density of the chemical bonds, each with a dipole of  $e^2d_{MS}$ ,  $d_{MS}$  is the distance between metal and semiconductor atoms at the interface,  $\varepsilon_{it}$  is the dielectric screening constant and  $\kappa$  is the sum of all the hopping interactions.

In this model, the ISR was considered as a molecule. A few planes of atoms each from the semiconductor and metal lattices are included in this molecule, consisting a total of  $N_M$  metal atoms and  $N_S$  semiconductor atoms, each one with the other form the chemical bonds  $N_B$  as shown in Figure.1.8 In general,  $N_B$  need not equal, and is likely less than the total number of semiconductor (or metal) atoms per unit area of the interface. Lattice mismatch, structure incompatibility, the formation of tilted bonds, etc., all tend to reduce the number of effective bonds formed across an MS interface. Charge transfer is assumed to occur only between atoms directly involved in the interface bonds.

Figure 1.8: A cross-sectional view of the model of a metal semiconductor interface used in the bond polarization theory.

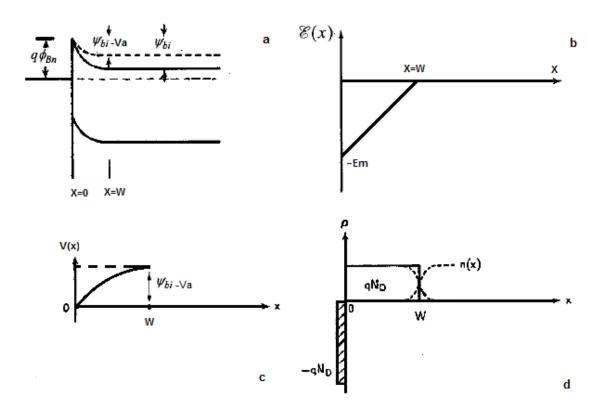

#### 1.1.2. Depletion region

To find the spatial distributions of potential and electric fields, the depletion layer width of a Schottky diode, one needs to solve the Poisson equation in the depletion region using proper boundary conditions. The one-dimensional Poisson equation in the depletion region of a Schottky diode is given by

$$\frac{d^2V(x)}{dx^2} = -\frac{\rho}{\varepsilon_0 \varepsilon_s} \tag{1.9}$$

Where  $\varepsilon_0$  is the permittivity of free space, and  $\varepsilon_S$  is the dielectric constant of the semiconductor. The charge density for  $0 \le x \le W$  is given by

$$\rho = q[N_D - n(x)] \tag{1.10}$$

Where n(x) is the electron density in the space charge region and it is decrease exponentially with distance from the depletion layer edge into the space charge region. Using a one-sided abrupt junction approximation one can obtain the spatial distribution of the electric field by integrating equation (1.9) once, with the result

$$E(x) = -\frac{dV(x)}{dx} = \left(\frac{qN_D}{\varepsilon_0 \varepsilon_s}\right) x + C1 \tag{1.11}$$

The constants C1 can be determined using the following boundary conditions:

$$E(x) = 0 \quad at \quad x = W \tag{1.12}$$

By substituting C1 into equation (1.11), one obtains the spatial distributions of the electric field inside the depletion region, which is given by:

$$E(x) = \left(\frac{qN_D}{\varepsilon_0 \varepsilon_s}\right)(x - W) \tag{1.13}$$

The potential distribution can be obtained by integrating equation (1.13) taking the interface as the potentials origin, which yields

$$V(x) = -\left(\frac{qN_D}{\varepsilon_0\varepsilon_S}\right)\left(\frac{x^2}{2} - Wx\right) \tag{1.14}$$

The depletion layer width W can be expressed in terms of ND,  $V_{bi}$ , and Va (applied voltage) across the barrier. From Figure (1.9.a) a and equation (1.14) one obtains the potential at x = W as

$$V(x = W) = V_{bi} - V_a = \frac{qN_DW^2}{\varepsilon_0\varepsilon_s}$$

(1.15)

From eq.2.15, the depletion layer width W is given by

$$W = \sqrt{\frac{2\varepsilon_0 \varepsilon_s (V_{bi} - V_a)}{q N_D}}$$

(1.16)

It is seen from equation (1.16) that the depletion layer width is directly proportional to the square root of the applied voltage (Va), and is inversely proportional to the square root of the dopant density of the semiconductor. Furthermore, equation (1.16) shows that the depletion layer width decreases with the square root of the forward-bias voltage (i.e., for  $Va \ge 0$ ), and increases with the square root of the reverse-bias voltage (i.e., for Va < 0) [32,41].

The previous approximation is valid for  $V_{bi}kT/q \gg 1$ . Therefore (2.) is corrected to [42]

$$W = \sqrt{\frac{2\varepsilon_0 \varepsilon_s (V_{bi} - V_a - \frac{kT}{q})}{qN_D}}$$

(1.17)

Figure 1.9: (a) Energy band diagram, (b) electric field, (c) potential distribution, and (b) space-charge distribution for a metal/n-type semiconductor Schottky barrier diode.

#### 1.1.3. Capacitance

From Figure (1.9.d) the total space charge Q (per unit area) in the depletion region is

$$Q = qN_DW = \sqrt{2qN_D\varepsilon_0\varepsilon_s(V_{bi} - V_a - \frac{kT}{q})}$$

(1.18)

To take into account the charges resulting from the traps in the depletion region,  $N_D$  must be replaced by  $N_{SCR}$  (ionized impurity in the space charge region).  $N_{SCR} = N_D^+ \mp (n, p)_T^{-,+}$ , where  $n_T^-$  are deep-level or shallow-level acceptors occupied by electrons, and  $P_T^+$  are deep-level or shallow-level donors occupied by holes [43].

The depletion layer capacitance (junction capacitance) per unit area can be obtained by differentiating equation (1.18) with respect to the applied voltage (C = |dQ/dV|), which yields

$$C_d = \frac{dQ}{dV_a} = \sqrt{\frac{qN_{SCR}\varepsilon_0\varepsilon_s}{2\left(V_{bi} - V_a - \frac{kT}{q}\right)}}$$

(1.19)

Equation (1.19) can also be written as

$$\frac{1}{C_d^2} = \frac{2\left(V_{bi} - V_a - \frac{kT}{q}\right)}{qN_{SCR}\varepsilon_0\varepsilon_S} \tag{1.20}$$

By plotting  $1/C_d^2$  as a function of applied voltage we can find the doping concentration and built-in voltage  $V_{bi}$ . If the doping concentration is homogeneous the plot should be linear.  $V_{bi} = V' + (kT/q)$ , where V' is the extrapolation to the voltage axis such that  $1/C_d = 0$ . The doping concentration can be determined from the slop via [42]

$$N_{SCR} = \frac{2}{q\varepsilon_0 \varepsilon_s} \left[ \frac{1}{d(C_d^2)/dV} \right]$$

(1.21)

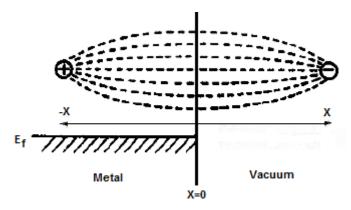

## 1.1.4. Schottky effect

The image-force lowering, also known as the Schottky effect or Schottky-barrier lowering, is the image-force-induced lowering of the barrier energy for charge carrier emission, in the presence of an electric field. When an electric field is applied to the metal surface, electrons that escape from the metal surface to a distance x in vacuum will create an electric that is same as if an image charge, +q is located at -x from the metal surface (Figure 1.10).

Figure 1.10: The induce image charge inside the metal of Schottky effect.

The positive image charges create a Coulomb attractive force (image force), which tends to pull the escaping electrons back into the metal. The image force can be expressed by

$$F_i = \frac{q^2}{16\pi\varepsilon_0 x^2} \tag{1.22}$$

The potential energy associated with this image force is given by

$$V_i(x) = -\int_{-\infty}^{x} F_i dx = -\frac{q^2}{16\pi\varepsilon_0 x^2}$$

(1.23)

The potential energy due to the applied electric field can be written as

$$V_a(x) = -qE_x \qquad \text{(for x \leftarrow W)}$$

The total potential energy PE as a function of distance is given by the sum

$$V_i(x) + V_a(x) = -\frac{q^2}{16\pi\varepsilon_0 x^2} - qE_x$$

(1.25)

The maximum potential energy and the distance where the maximum potential occurs are obtained by differentiating eq. 1.25 with respect to x and then setting the result equal to 0, which yields

$$x_m = -\frac{q^2}{16\pi\varepsilon_0 E} \tag{1.26}$$

Figure 1.11: Energy band diagram showing Schottky effect at: (a) metal-vacuum interface in the presence of an applied electric field (b) metal-semiconductor interface under different biasing condition.

And

$$V_{m(x_m)} = -q \sqrt{\frac{qE}{4\pi\varepsilon_0}} = -2qEx_m = -q\Delta\phi_m$$

(1.27)

These results can be applied to metal-semiconductor systems. However, the field should be replaced by the appropriate field at the interface, and the free-space permittivity  $\varepsilon_0$  should be replaced by an appropriate permittivity  $\varepsilon_s$ , characterizing the semiconductor medium, that is,

$$-q\Delta \emptyset = -q\sqrt{\frac{qE_m}{4\pi\varepsilon_s}} \tag{1.28}$$

As shown in Figure (1.11.b) the Schottky effect still occurs even when there is no bias because the electric field is not zero due to the built-in potential. However, the effect of image force lowering is smaller than that in a corresponding metal-vacuum system due to the large values of  $\varepsilon_s$  [34,41].

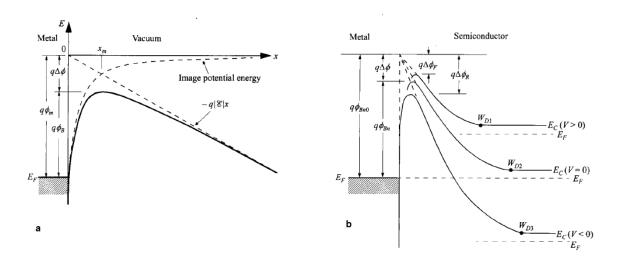

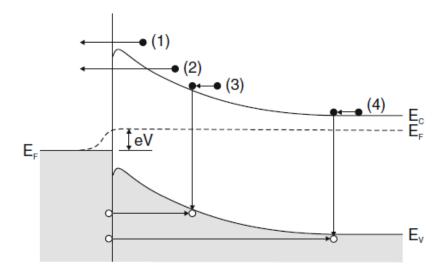

#### 1.1.5. Carrier transport mechanisms

The transport through a Schottky junction is dominated by the majority charge carriers, I.e. electrons (holes) in the case of an n-type (p-type) semiconductors, respectively. Figure.1.12 shows the basic transport mechanisms that can contribute to the total current: (1) emission of electrons over the barrier, (2) tunneling through the barrier (3) recombination in the depletion region (4) hole injection from metal. Vérifier

Figure 1.12: The basic transport mechanisms at metal-semiconductor junction.

The transport of electrons above the barrier is the dominant process for ideal Schottky with moderately doped semiconductors operated at moderate or high temperatures. This process was described by three theory, diffusion of Schottky [44], thermionic emission (TE) of Bethe [45] and thermionic emission diffusion (TED) of Sze and Crowell [46]. The current density expressions of the diffusion and thermionic-emission theories, are basically very similar, while TED theory is a combination of the two theories. Here we will discuss thermionic emission theory since it is the most widely used in the interpretation of the experimental I-V characteristics Schottky barrier diodes.

#### a. Thermionic emission:

The thermionic emission theory is derived by using the assumptions that the barrier height is much larger than kT, so that the Maxwell-Boltzmann approximation applies and that thermal equilibrium is not affected by this process. The current density from the semiconductor to the metal  $J_{s\to m}$  is then given by the concentration of electrons with energies sufficient to overcome the potential barrier

$$J_{s\to m} = \int_{E_{Fn} + q\phi_{bn}}^{\infty} q v_x dn \tag{1.29}$$

#### Chapter 1: Schottky barrier diode and InP properties

Where  $E_{Fn} + q\phi_{bn}$ , is the minimum energy required for thermionic emission into the metal, and  $v_x$  is the carrier velocity in the direction of transport. The electron density in an incremental energy range is given by

$$dn = N(E)F(E)dE (1.30)$$

Where N(E) and F(E) are the density of states and the distribution function, respectively.

$$dn \approx \frac{4\pi (2m^*)^{3/2}}{h^3} \sqrt{E - E_C} exp\left(-\frac{E - E_C + q\phi_{bn}}{kT}\right) dE$$

(1.31)

For a given energy E, the carrier velocity v is determined by

$$E = E_C + \frac{1}{2}m^*v^2 (1.32)$$

Thus, we obtain

$$\sqrt{E - E_C} = v \sqrt{\frac{m^*}{2}} \tag{1.33}$$

And

$$dE = m^* v \, dv \tag{1.34}$$

Therefore, we write equation (1.31)

$$dn \approx 2\left(\frac{m^*}{h}\right)^3 exp\left(-\frac{q\phi_{bn}}{kT}\right) exp\left(-\frac{m^*v^2}{2kT}\right) (4\pi v^2 dv)$$

(1.35)

Then the one-dimensional integral over  $4\pi v^2 dv$  is converted into a three-fold integral over. Integration over all velocities in y and z directions yields a factor  $2\pi kT/m^*$ . The integration over  $v_x$  runs from the minimum velocity  $v_{0x}$  necessary to pass the barrier

$$\int_{v_{0x}}^{\infty} exp\left(-\frac{m^* v_x^2}{2kT}\right) v_x dv_x = \frac{kT}{m^*} exp\left(-\frac{m^* v_{x0}^2}{2kT}\right)$$

(1.36)

With the minimum velocity determined by

$$\frac{1}{2}m^*v_{0x}^2 = q(V_{bi} - V) (1.37)$$

Substituting (2.) into (2.) yields

Chapter 1: Schottky barrier diode and InP properties

$$J_{s\to m} = \left(\frac{4\pi q m^* k^2}{h^3}\right) T^2 exp\left(-\frac{q \phi_{bn}}{kT}\right) exp\left(\frac{q V}{kT}\right)$$

(1.38)

Where  $\frac{4\pi q m^* k^2}{h^3}$  called Richardson constant  $(A^*)$  and can be rewritten as

$$\frac{4\pi q m_0 k^2}{h^3} \frac{m^*}{m_0} = 120 \frac{m^*}{m_0} Acm^{-2} k^{-2}$$

(1.39)

This current duo to the transport of electrons from semiconductor to metal increase in the forward bias and decrease in the reverse bias duo to the decrease and the increase of the barrier respectively. While the current duo to the transport of electrons from metal to semiconductor  $(J_{m\to s})$  does not depend on bias, because the barrier remains constant if we neglect the Schottky effect. Therefore  $J_{m\to s}$  can be obtained from the condition  $j=J_{s\to m}+J_{m\to s}=0$  for zero bias. Therefore, the total current density in the thermionic-emission model is

$$J = A^*T^2 exp\left(-\frac{q\phi_{bn}}{kT}\right) \left[exp\left(\frac{qV}{kT}\right) - 1\right]$$

(1.40)

Where  $\left[A^*T^2exp\left(-\frac{q\phi_{bn}}{kT}\right)\right]$  is the saturation current density  $(j_s)$ .

Multiplying the saturation current density by the surface of the diode (A), the saturation current density  $j_s$  and current density J (A/cm<sup>2</sup>) becomes the saturation current  $I_s$  and the current I (A) respectively.

To take into account the effect of the series resistance (R<sub>S</sub>) associated with the bulk material in the semiconductor and the ohmic back contact, and other phenomena that deviate the I-V characteristic from the ideal form such, Schottky effect, equation (1.40) is modified to [47]

$$I = I_s \left[ exp\left(\frac{q(V - R_S I)}{nkT}\right) - 1 \right]$$

(1.41)

Where n is the ideality factor.

## b. Tunneling:

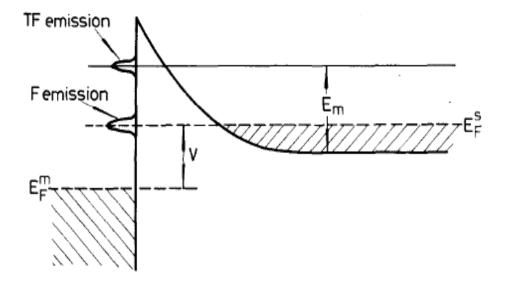

Tunneling of electrons thought the barrier potential is an important phenomenon which can dominate the transport process in certain conditions. In contrary of classical physics, the particles in quantum physics can escape the barrier potential even if its energy is below the maximum of this potential. There is two physical models describing the tunneling phenomenon (Figure 2.13), thermionic field emission (TFE) and field emission (FE).

Figure 1.13: Field and thermionic-field emission under forward bias.

Field emission is a pure tunneling process and occur in the case of a degenerate semiconductor at low temperature, where the donor density is so high, and the potential barrier so thin, the current arises from electrons with energies close to the Fermi energy. While thermionic field-emission is tunneling of thermally excited carrier and occur at higher temperature, electrons are excited to higher energies, and the tunneling probability increases very rapidly because the electrons 'see' a thinner and lower barrier. On the other hand, the number of electrons having a particular energy decreases very rapidly with increasing energy, and there will be a maximum contribution to the current from electrons which have an energy above the bottom of the conduction band [48]. According to Padovani and Stratton [49] FE and TEF current can be expressed as

#### I. forward bias:

$$J = J_s \exp\left(\frac{E}{E_{00}}\right) \tag{1.42}$$

Where  $J_s$  is the saturation current density given by

$$J_{s(FE)} = \frac{2\pi A^* E_{00} \exp(-E_B/E_{00})}{kT \left[ \log \left\{ 2 \left( \frac{E_B - E}{\xi_2} \right) \right\} \right] \sin \left[ \frac{\pi kT}{2E_{00}} \log \left\{ 2 \left( \frac{E_B - E}{\xi_2} \right) \right\} \right]}$$

(1.43)

$$J_{s(TFE)} = \frac{A^* \left(\pi E_{00} (E_B - E + \xi_2)\right)^{1/2}}{kT \cosh(E_{00}/kT)} exp\left[\frac{\xi_2}{kT} - \frac{E_B + \xi_2}{E_0}\right]$$

(1.44)

#### II. reverse bias:

$$J_{(FE)} = \frac{A^* \pi E_{00} exp \left[ -2E_B^{3/2} / 3E_{00} (E_B - E)^{1/2} \right]}{kT \left[ E_B / (E_B - E) \right]^{1/2} \sin \left\{ \pi kT \frac{\left[ E_B / (E_B - E) \right]^{1/2}}{E_{00}} \right\}}$$

(1.45)

$$J_{(TFE)} = \frac{A^* (\pi E_{00})^{1/2}}{kT} \left[ -E + \frac{E_B}{\operatorname{csch}^2(E_{00}/kT)} \right]^{1/2} exp\left( -\frac{E_B}{E_0} \right)$$

(1.46)

Where  $E_B$  is the potential energy of the top of the barrier with respect to the Fermi level of the metal, E is the potential energy associated with an applied bias V,  $\xi_2$  is the energy of the Fermi level of the semiconductor measured with respect to the bottom of the conduction band,  $A^*$  is the effective Richardson constant of the semiconductor and the metal in the case of forward bias and reverse bias respectively,  $E_0$  and  $E_{00}$  are the energy given b

$$E_{00} = \frac{q\hbar}{2} \sqrt{\frac{N}{m^* \mathcal{E}_s}} \tag{1.47}$$

$$E_0 = E_{00} \cosh(E_{00}/kT) \tag{1.48}$$

By comparing the thermal energy kT to  $E_{00}$  (characteristic tunnelling energy that is related to the tunnel effect transmission probability) one can predict the dominant transport process. When  $kT \gg E_{00}$  TE dominates, when  $kT \ll E_{00}$  FE dominates and when  $kT \approx E_{00}$  TFE is the main mechanism which is a combination of TE and TFE.

#### 1.1.6. barrier inhomogeneities:

Schottky barrier height inhomogeneities can be defined as the lateral variation of the barrier height (along the interface), this lateral variation was attributed to interface propriety and the fabrication process [50-52]. Evidence for the presence of inhomogeneity in the SBH's was

recognized and reported only sporadically before the 1990 [53, 54], the inhomogeneities was described by two parallel diodes with different barrier height and the junction current is a sum of the contribution from the two diodes. These models is in signification error when the SBH varies spatially on a scale less than, or comparable to the width of the space-charge region. The development of the ballistic electron emission microscopy (BEEM) technique [55, 56], provided the spatial resolution needed to examine the distribution of local SBH underneath ultrathin metal layers. Occasionally, large-scale variations (0.7–1.1 eV) of the SBH were observed at compound semiconductor [57]. After 1990 more sophisticated models were developed. Werner and Guttler model [17] and Tung model [16] are discussed next.

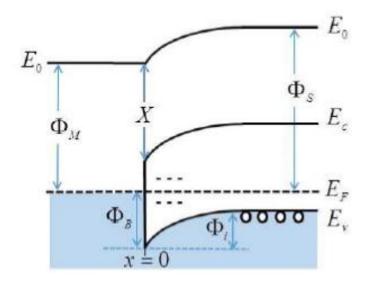

#### a. Werner and Guttler model

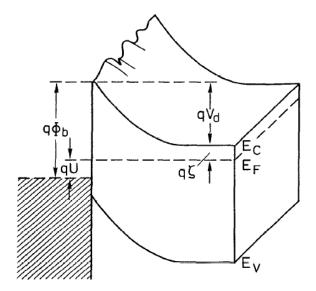

The model considered a large area device which contain potential fluctuation or barrier inhomogeneities at the MS interface Figure (1.14) on length a scale, and this potential fluctuation is smaller than the width of the space-charge region, i.e.,  $< 1 \mu m$ .

Figure 1.14: Two-dimensional band diagram of an inhomogeneous Schottky contact.

The potential fluctuation was described by a Gaussian distribution of the potential  $P(V_d)$  with a standard deviation  $\sigma_s$  around a mean  $\bar{V}_d$  value according to

$$P(V_d) = \frac{1}{\sigma_s \sqrt{2\pi}} e^{-(\bar{V}_d - V_d)^2 / (2\sigma_s^2)}$$

(2.49)

By replacing the homogeneous potential in thermionic emission theory with  $P(V_d)$  and do the integral over the range  $[-\infty, +\infty]$  for  $J_{s\to m}$  and  $J_{m\to s}$ , Werner and Guttler found respectively

$$V_d = \bar{V}_d - \frac{q\sigma_s^2}{2kT} \tag{1.50}$$

$$\emptyset_{b0} = \overline{\emptyset}_{b0} - \frac{q\sigma_s^2}{2kT} \tag{1.51}$$

Than the total current through the inhomogeneous interface is given by

$$I = AA^*T^2 exp\left(-\beta \left(\overline{\phi}_{b0} - \frac{q\sigma_s^2}{2kT}\right)\right) \left[exp\left(\frac{qV}{kT}\right) - 1\right]$$

(1.52)

Where

$$I_{s} = AA^{*}T^{2}exp\left(-\beta\left(\overline{\emptyset}_{b0} - \frac{q\sigma_{s}^{2}}{2kT}\right)\right)$$

(1.53)

While the capacitance was found to be insensitive to the potential fluctuation that are less than the width of the space charge region, in other words the capacitance depends only on the mean band banding  $\overline{V}_d$  and is insensitive to the standard deviation  $\sigma_s$  of the barrier distribution. Thus,  $V^C{}_d = \overline{V}_d$  and  $\emptyset^C{}_b = \overline{\emptyset}_{b0}$ . This result explains the differences of barrier which are derived from capacitance and current.

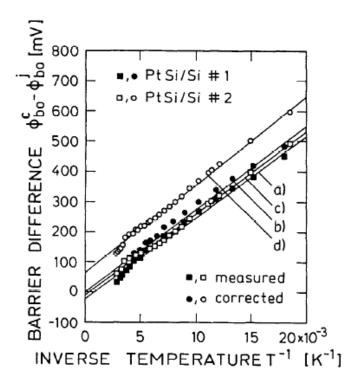

The authors propose two plots to evaluate the experimental results. The first is the plot of  $(\emptyset^C_b - \emptyset^j_b)$  Vs  $T^{-1}$ , the plot should yield a straight line. From this plot the standard deviation  $\sigma_s$  can be determined, where the mean barrier  $\overline{\emptyset}_b$  is equal to  $\emptyset^C_b$ .

Since the y-axis intercepts of curve (a) and (b) in Figure.1.15 don not exactly equal zero as predicted by Eq.1.51 The authors ascribed this finding to the temperature dependence of  $\sigma_s$  according to

$$\sigma_{s}^{2}(T) = \sigma_{s}^{2}(T=0) + \alpha_{\sigma}T$$

(1.54)

Where the slope equal to  $q\sigma_s^2(T=0)/(2k)$  and the y-axis intercept  $q\alpha_\sigma/2k$ .

Schottky mean barrier itself varies also approximately linearly with T according to

$$\overline{\emptyset}_b(T) = \overline{\emptyset}_b(T=0) + \alpha_{\overline{\emptyset}}T \tag{1.55}$$

Where can  $\alpha_{\overline{0}}$  obtained from the slop of  $\emptyset^C_b$  *Vs T* plot.

Figure 1.15: Plot of differences between Schottky barriers for two PtSi/Si diodes. Curves (a) and (c) show the difference between values as derived from the conventional evaluation of I/U and C/U data. Curves (b) and (d) follow from curves (a) and (c) after correcting the capacitance barrier for the bias dependence of the mean Schottky barrier according to equation (1.57).

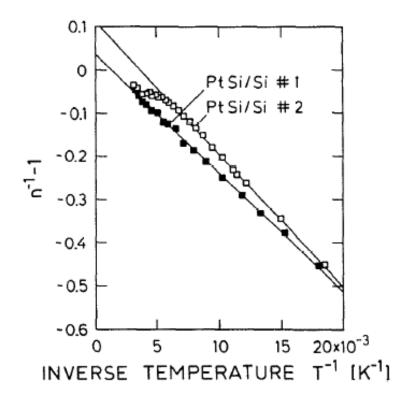

The second is a plot of  $(n^{-1} - 1)$  Vs  $T^{-1}$ . This plot is based on the equation that predicts the temperature dependence of the ideality factor n of inhomogeneous Schottky contacts or so called  $T_0$  problem, the equation is given by

$$n^{-1} - 1 = -\rho_2 + \frac{q\rho_3}{2kT} \tag{1.56}$$

Where  $\rho_2$  and  $\rho_3$  are the voltage coefficients  $\overline{\emptyset}_b$  (quantify the voltage deformation of the barrier distribution) and can be obtained from the intercept and the slope respectively.

The mean barrier and standard deviation bias dependent are given by [50]

$$\overline{\emptyset}_b - \overline{\emptyset}_{b0} = \rho_2 U \tag{1.57}$$

$$\sigma_s - \sigma_{s0} = \rho_3 U \tag{1.58}$$

Figure 1.16: The temperature-dependent ideality data of our PtSi/Si diodes follow equation (1.56).

The authors were able to fit several experimental data for Schottky contacts on Si, GaAs, and InP. In addition, the most experiments in the last two decades such as [8, 12, 14, 18, 19], were used this model to interpret the barrier and the ideality factor temperature dependence.

The demerits of this model are absence of interaction between small low barrier regions, the physical reason for the variation of parameters with bias, also the model does not address the length scale of the small low barrier regions [16].

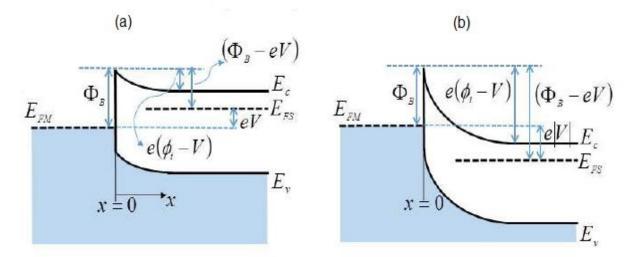

#### b. Tung model

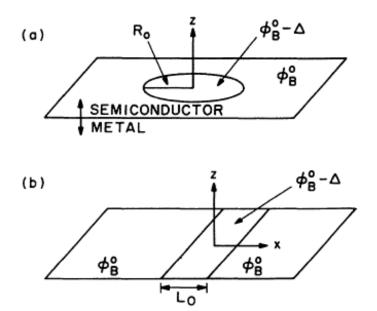

A cording to Tung [16], the barrier inhomogeneities is a result of the presence of small regions with a low SBH ( $\emptyset_{b0} - \Delta$ ) embedded in an interface with an otherwise uniform high SBH ( $\emptyset_{b0}$ ). Two geometries were considered for the low-SBH region, a small circular patches and narrow semi-infinite strips, as shown schematically in Figure (1.16).

Figure 1.17: Geometries and coordinates of examples of the inhomogeneities in Tung model.

(a) Circular patch, (b) narrow strip.

As seen in Figure.1.16, the small regions with low SBH are characterized by two important parameters, the value of the barrier which is lower than the uniform barrier by a value  $\Delta$  (eV), and the second parameter is the radius  $R_0$  or the length  $L_0$  (for the circular patches and semi-infinite strips respectively) which represent the surface of the small regions with low SBH. The potential around the circular patch and the narrow strip are given by next equations

$$V(\rho, Z) = V_{bb} \left( 1 - \frac{Z}{W} \right)^2 - V_n + V_a - \frac{V_{bb} \Gamma^3 z W^2}{(z^2 + \rho^2)^{3/2}}$$

(1.59)

$$V(x, y, Z) = V_{bb} \left( 1 - \frac{z}{W} \right)^2 - V_n + V_a - \frac{2V_{bb}\Omega^2 zW}{x^2 + z^2}$$

(1.60)

Where  $V_{bb}$  is the built-in potential of the uniform barrier as function of the applied bias  $(V_{bb} = V_{bi} - V_a)$ ,  $V_n$  is the difference between the FL and the conduction band maximum (CBM),  $\rho$  is the radial coordinate,  $\Gamma$  and  $\Omega$  are a dimensionless quantity that measures the strength of the patch and the strip respectively.

$$\Gamma^3 = \frac{\Delta R_0^2}{2V_{bb}W^2} \tag{1.61}$$

$$\Omega^2 = \frac{\Delta L_0}{2\pi V_{hh} W} \tag{1.62}$$

In contrary of the previous model, Tung model take in to account the length scale of the inhomogeneities by introducing the radius  $R_0$  and the length  $L_0$  of the patch and the strip in the potential equation. In addition, it takes in to account the interaction between the small low barriers regions by phenomenon called pinch-off.

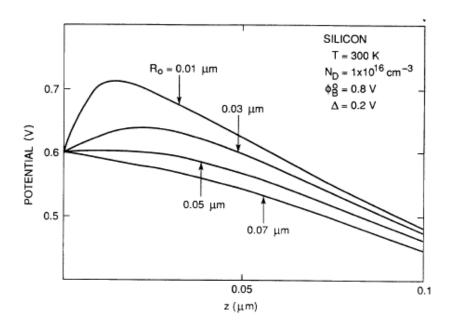

A small low barrier region is said to be pinched-off if the carrier need to go over a potential of a neighbour region that has a higher potential. For a large  $\Delta$ , or smal  $R_0$ , the potential in front of the patch is obviously pinched-off. Figure 1.17 illustrates the pinch-off effect by plotting the potential close to a low-SBH patch as a function of the radius  $R_0$ , the patch has a  $\Delta$ = 0.2 (eV) and the uniform barrier of the diode  $\emptyset_{b0} = 0.8$  (eV), which mean that the barrier of the patch equal to 0.6 (eV) ( $\emptyset_{b0} - \Delta$ ). When the patch's radius has a large value (0.07 um) the potential in close to the patch is equal to the barrier of the patch (0.6 eV), when the patch's radius be smaller the potential in close to the patch reaches a value close to the uniform barrier value (0.8 eV).

Figure 1.18. CBM potentials along the z axis in close to a low-SBH patch, illustrating the influence of the radius of a low-SBH patch on potential pinch-off.

The condition for pinch-off is obtained from eq.1.59 and eq.1.60 for the patch and the strip respectively

$$\frac{\Delta}{V_{hh}} > \frac{R_0^2}{W} \tag{1.63}$$

$$\frac{\Delta}{V_{bb}} > \frac{\pi L_0}{2W} \tag{1.64}$$

Effectively the total current of inhomogeneous diode is given by two formula depending on the density distribution type of the patches as a function of the parameter  $\gamma$ . Where  $\gamma$  is a constant related to the patch characteristics (a true parameter of the MS interface inhomogeneity) and is given by

$$\gamma = 3\left(\frac{\Delta R_0^2}{4}\right)^{\frac{1}{3}} (cm^{\frac{2}{3}}V^{\frac{1}{3}}) \tag{1.65}$$

The most used expression in the interpretation of experimental results [24-28] is based on one-half of a Gaussian distribution. The density of patches with their parameter  $\gamma$  lying between  $\gamma$  and  $\gamma + d\gamma$  is  $N(\gamma)d\gamma$ :

$$N(\gamma) = \begin{cases} \frac{\sqrt{2}C_1}{\sqrt{\pi}\sigma_1} exp\left(-\frac{\gamma^2}{2\sigma_1^2}\right), & \gamma > 0\\ 0, & \gamma < 0 \end{cases}$$

(1.66)

Where  $\sigma_1$   $\left(cm^{\frac{2}{3}}V^{\frac{1}{3}}\right)$  is the standard deviation and  $C_1$   $(cm^{-2})$  is the total density of patches. The strip also has a parameter  $\omega$  and  $N(\omega)$  similar to the parameter  $\gamma$  and  $N(\gamma)$  of the patch respectively.

The total current at any given bias is approximately given by

$$I_{total} = A^*AT^2 exp(-\beta \phi_{b0}) [exp(\beta V_a) - 1] [1 + f(V_{bb}) exp(\beta^2 \kappa V_{bb}^{\xi})]$$

(1.67)

Where  $\beta = q/kT$ , the constants  $\kappa$  and  $\xi$  and the slowly varying function f are defined in Tab.1.1

Table 1.1: Parameters for electron transport at an inhomogeneous SB with one-half of a Gaussian distribution

| Parameter          | Patch                                               | Strip                                                                                |

|--------------------|-----------------------------------------------------|--------------------------------------------------------------------------------------|

| ξ                  | $\frac{2}{3}$                                       | $\frac{1}{2}$                                                                        |

| κ                  | $\frac{\sigma_1^2}{2\eta^{2/3}}$                    | $\frac{\sigma_2^2}{2\eta^{1/2}}$                                                     |

| $f(\beta, V_{bb})$ | $\frac{8C_1\sigma_1^2\pi\eta^{1/3}}{9V_{bb}^{1/3}}$ | $\frac{C_2 \sigma_2^{2/3} \pi \sqrt{\beta} \eta^{1/8} L_{strip}}{1.46 V_{bb}^{1/8}}$ |

Where

$$\eta = \varepsilon_s/(qN_d)$$

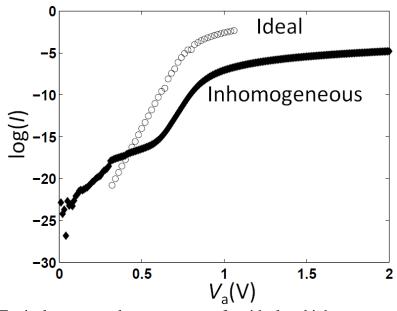

The current in equation (1.67) is made up of two components: one being the current over the entire diode, which has a uniform SBH of  $\emptyset_{b0}$  and represented by 1 in the last term of equation (1.67), this current dominates at high temperatures and displays near unity ideality factor. The other term represents an additional current due to the presence of the low-SBH patches or strips, at low temperatures this term becomes much larger than 1, and the low-SBH patches dominate at small bias and the ideality factor is larger than 1. In addition, the effect of patches on the I-V characteristic of the diode can be seen clearly, in the reverse bias the current never saturates, while in the forward bias at small values the I-V characteristic shows a curvature or a double diode behaviour Figure (1.19).

One can remark that the parameter  $\gamma$  does not appeared in the total current equation, but is present indirectly by  $\sigma_1$  which have the same unit.

Figure 1.19: Typical current-voltage response of an ideal and inhomogeneous diode [58]

The combined effect of all the low-SBH regions is as if there were a big low-SBH region in the diode with an effective area ( $A_{eff}$ ) and an effective SBH ( $\emptyset_{eff}$ ).

Even though the effective SBH of each individual patch is roughly temperature independent, but together they may be represented by a temperature dependent effective SBH. That is, at each temperature the current flow through some patches with identical  $\gamma$ .  $A_{eff}$  and  $\emptyset_{eff}$  of the patches are given by the following relations [25]

$$\emptyset_{eff} = \emptyset_{b0} - \frac{\sigma_1^2}{2kT} \left(\frac{V_{bb}}{\eta}\right)^{\frac{2}{3}}$$

(1.68)

$$A_{eff} = A C_1 A_p \tag{1.69}$$

Where  $A_P$  is the effective area of one patch and is given by

$$A_p = \frac{8\pi\sigma_1^2}{9} \left(\frac{\eta}{V_{bb}}\right)^{1/3} \tag{1.70}$$

From equation (1.68) and equation (1.70)  $A_P$  can be rewritten as

$$A_{p} = \frac{8\pi(2kT)}{9} \left(\frac{\eta}{V_{bb}}\right) (\emptyset_{b0} - \emptyset_{eff})$$

(1.71)

#### 1.2 Material property of indium phusphyde

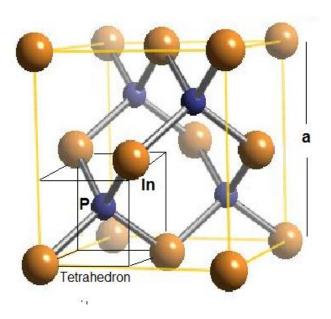

#### 1.2.1 Cristal structure:

Figure 1.20: Zinc-blende structure for Indium Phosphide

Indium Phosphide (InP) belong to the family of compound semiconductor of III-V groups with Zinc-blende crystal structure like the most III-V group semiconductors, the Zinc-blend structure is similar to the diamond structure except that the two FCC sub-lattices are occupied alternately by two different kinds of atoms (In and P) as shown in Figure 1.20 [41].

## 1.2.2 Energy band structure:

One of the advantages of InP as III-V group semiconductor over silicon is its direct band gap, which gives strong absorption/emission characteristics that in different optoelectronic devices [1]. The appropriate combination of the band-gap value (1.34 eV at 300 K) and the high atomic numbers Z (49/15) is an advantage of InP over some other compound semiconductors, especially in view of the fabrication of highly efficient photon detectors operating within the temperature range 200–300 K. For example, InP exhibits an absorption efficiency about 3 times higher than GaAs regarding the photons with energy up to 150 keV [59]. The energy band gap structure of InP is shown in Figure (1.21).

Figure 1.21: Energy band gap structure of InP at 300 K.

#### 1.2.3 Electrical properties:

Concerning the electrical property InP has a very high electron mobility which makes it a particularly attractive material for a steadily increasing number of applications in optoelectronics, high-speed microelectronics and solar-cell devices [2]. Moreover InP offers potentially a fastest operation rate due to its higher electron drift velocity in the electric field region (about 10<sup>4</sup> V/cm) mostly used for detector operation, and this value increases at low temperature and is higher by several times than is offered by GaAs working in the saturation drift velocity regime [59]. Furthermore, InP is more radiation resistant than Si and GaAs, this

is a very important advantage not only to space solar cells but also to the electrical property, because the radiation can affect the mobility and the carrier diffusion length [4, 60]. Table (1.2) shows several important parameters used in the simulation.

Table 1.2: Important parameters of InP at 300 K

| Parameter                                         |                    | Value                      | Unit                                  |

|---------------------------------------------------|--------------------|----------------------------|---------------------------------------|

| Effective mass                                    | Electron $m_n/m_0$ | 0.08 [63]                  |                                       |

|                                                   | Hole $m_p/m_0$     | 0.69 [63]                  |                                       |

| Richardson constant                               | N-type             | 9.6 [63]                   | A K <sup>-2</sup><br>cm <sup>-2</sup> |

|                                                   | P-type             | 82.8 [63]                  | CIII                                  |

| Affinity                                          |                    | 4.38 [63]                  | eV                                    |

| Dielectric constant $\varepsilon_s/\varepsilon_0$ |                    | 12.5 [63]                  |                                       |

| Effective density of stats                        | СВ                 | 5.7 10 <sup>17</sup> [61]  | cm <sup>-3</sup>                      |

|                                                   | VB                 | 1.1 10 <sup>19</sup> [61]  |                                       |

| Thermal velocity                                  | Electron           | $3.9 \ 10^5 \ [61]$        | m s- <sup>1</sup>                     |

|                                                   | Hole               | $1.7 \ 10^5 \ [61]$        |                                       |

| Auger coefficient                                 | Electron           | 3.7 10 <sup>-31</sup> [61] | $Cm^6 s^{-1}$                         |

|                                                   | Hole               | 8.8 10 <sup>-30</sup> [61] |                                       |

## **1.2.4 Doping:**