الجمهورية الجزائرية الديمقر اطية الشعبية République Algérienne Démocratique et Populaire وزارة التعليم العالي والبحث العلمي Ministère de l'Enseignement Supérieur et de la Recherche Scientifique

Université Mohamed Khider – Biskra Faculté des Sciences Exactes et Sciences de la Nature et de la Vie Vice Doyen Chargé de la Post-Graduation de la Recherche Scientifique et des Relations extérieur

جامعة محمد خيضر بسكرة كلية علوم الدقيقة وعلوم الطبيعة والحياة نيابة العمادة المكلفة بما بعد التدرج والبحث العلمى والعلاقات الخارجية

Thèse présentée en vue de l'obtention du diplôme de

# **Doctorat en Science**

Spécialité ou option: Physique

# Simulation bidimensionnelle de l'effet des pièges profonds dans le substrat sur les caractéristiques des Transistors à Effet de Champ en Arséniure de Gallium (GaAs FETs)

(Two Dimensional Simulation of Deep Level Substrate Effect on the Characteristics of the GaAs Field Effect Transistor (GaAs FETs))

Présentée par

## Abdeslam Nora Amele

Le 14 Mai 2013

## Devant le jury composé de:

| Meftah Afak          | Professeur à l'Université de Biskra   | Présidente   |

|----------------------|---------------------------------------|--------------|

| Sengouga Nouredine   | Professeur à l'Université de Biskra   | Encadreur    |

| Mustapha C.E. Yagoub | Professeur à l'Université d'Ottawa.Ca | Co-Encadreur |

| Dehimi Lakhdar       | Professeur à l'Université de Batna    | Examinateur  |

| Ledra Mohammed       | M. C.A à C.U de Mila                  | Examinateur  |

| Hemaizia Zahra       | M. C.A à l'Université de Biskra       | Examinateur  |

#### Abstract

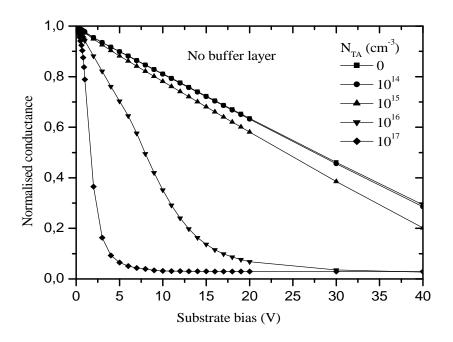

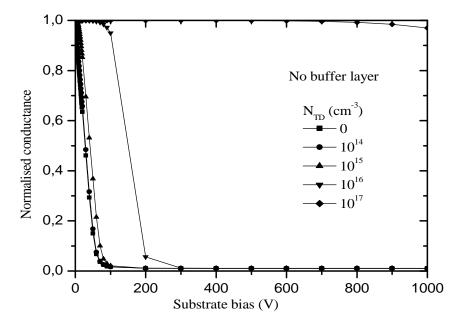

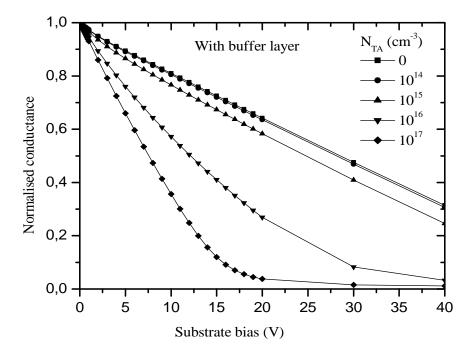

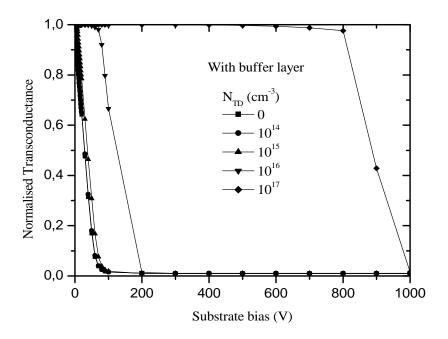

In this thesis, the reduction of the conductance of GaAs FETs by a negative voltage applied to the substrate, termed backgating or sidegating, was numerically modeled to determine which type of traps is responsible of this phenomenon. Drift diffusion Modelling was carried out for several sets of deep levels in the substrate. It has been observed that deep acceptors are mainly responsible for backgating, independently of the shallow level type in the substrate. In this case, there is no threshold. However, when deep donors are present in the substrate, backgating is again reduced but with a threshold. The presence of a buffer layer between the channel and the semi-insulating substrate also helps reducing backgating.

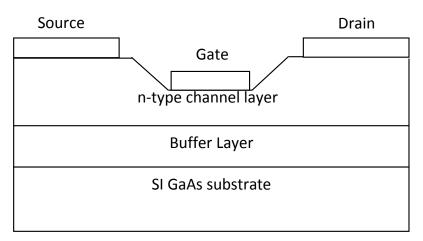

A two dimensional-hydrodynamic model was carried out to predict the performance of short-gate length power III–V field effect transistors. The model is based on the conservation equations, deduced from the Boltzmann transport equation and solved in their whole form. This model is also well suited to study the effect of substrate deep levels on the device. The results of hydrodynamic model (physical model) were compared to those of the fully distributed model (electrical model), especially, as for high frequency operating. In fact, at high frequencies, the dimensions of the electrodes of microwave transistors such as FETs become comparable to the wavelength, highlighting the parasitic effect of wave propagation. Thus, this effect needs to be accurately evaluated in the device model to assure a reliable design.

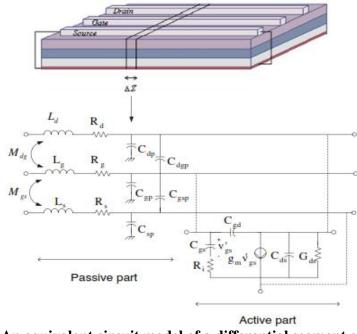

In the electrical model, the device width was then divided into an infinity number of segments, while each segment was considered as a combination of three coupled lines and a conventional FET equivalent circuit. By solving a set of multi-conductor transmission line equations using the Finite-Difference Time-Domain (FDTD) technique, an accurate and efficient transistor modeling approach was proposed.

Furthermore, the two dimensional hydrodynamic model had been shown to provide a valuable insight into the operation devices and confirm in many cases the measurements. Thus, the HDM model was used to study the effect of the gate length and its the recess depth on the recessed gate MESFET and pHEMT. It was found that, the performance of these devices is improved by shrinking the gate length and deepening the recess. The effect of increasing the delta doped density on the pHEMT performance was also studied. It is a way to improve the transfer efficiency of electrons from the delta-doped AlGaAs layer to the InGaAs channel. For the deep levels, it was found that deep acceptors improve the transistor performance while deep donors degraded it.

**Index Terms:** GaAs FETs, Backgating, deep traps, Hydrodynamic model, FDTD, time domain, wave effects.

#### Résumé

Dans cette thèse, la réduction de la conductance des transistors GaAs FETs par une tension négative appliquée au substrat (effet backgating ou sidegating) a été modélisée numériquement dans le but de préciser quel est le type de piège responsable de ce phénomène. La modélisation dérive-diffusion est effectuée pour plusieurs ensembles de niveaux profonds dans le substrat. Il a été observé que les accepteurs profonds sont principalement responsables du backgating et ce, indépendamment du type de niveau peu profond dans le substrat. Dans ce cas, il n'existe pas de seuil. Lorsque les niveaux donneurs profonds sont présents dans le substrat, on observe que cet effet est réduit avec une tension de seui. La présence d'une couche tampon entre le canal et le substrat semi-isolant contribue également à réduire l'effet backgating.

Le modèle hydrodynamique bidimensionnel est réalisé pour prédire les performances des transistors de puissance III-V à grille courte. Le modèle est basé sur les équations de conservation, déduites de l'équation de transport de Boltzmann, et résolues dans leur forme entière. Ce modèle est également bien adapté pour étudier les effets des niveaux profonds de substrat sur le dispositif. Les résultats du modèle hydrodynamique (modèle physique) ont été comparés à celui du modèle entièrement-distribué (modèle électrique), en particulier, dans le cas de fonctionnement en hautes fréquences où les dimensions des électrodes des transistors comme les FET deviennent comparables à la longueur d'onde, mettant en évidence l'effet parasite de la propagation des ondes. Ainsi, cet effet doit être évalué avec précision afin d'assurer une conception fiable.

Dans le modèle électrique, les électrodes des transistors ont été divisées en un nombre infini de segments, chaque segment étant considéré comme une combinaison de trois lignes de transmission couplées et d'un circuit équivalent FET classique. Les équations différentielles résultantes ont été résolues en utilisant la méthode des différences finies dans le domaine temporel, une approche temporelle précise et efficace de modélisation du transistor.

En outre, nous avons démontré l'aptitude du modèle hydrodynamique bidimensionnel de fournir des indications précieuses sur les caractéristiques des composants, indications confirmées par les mesures. Ainsi, le modèle HDM a été utilisé pour étudier l'effet de la longueur de la grille et la profondeur de son recess sur le MESFET à grille creusée et le pHEMT. Il a été constaté que les performances sont améliorées en réduisant la longueur de la grille et l'augmentation de son approfondissement. L'effet de l'augmentation de la densité de la couche delta-doped a été aussi étudié. En effet, ca améliore l'efficacité du transfert des électrons de la couche AlGaAs au canal InGaAs. Pour les niveaux profonds, il a été constaté que les accepteurs profonds améliorent les performances des transistors tandis que les donateurs profonds les dégradent.

**Mots Clés:** GaAs FETs, Backgating, pièges profonds, modèle Hydrodynamique, FDTD, domaine temporal, effets d'onde.

#### ملخص:

في هذه الرسالة تمت دراسة ( باستعمال النمذجة الرقمية)إنخفاض ناقليه الترانزستور ذوالتأثير الحقلي غاليوم أرسيند (GaAs FETs) بتطبيق جهد سالب على المسند و المعرّف ب Backgating أو Sidegating من أجل تعيين أي نوع من المستويات العميقة المسؤولة عن هذه الظاهرة.

تم استعمال نموذج جر – إنتشار لعدة مجموعات من المستويات العميقة الموجودة في المسند. لقد لوحظ أنّ المستويات الأخذة العميقة هي المسؤولة الأساسية عن ظاهرة backgating و بشكل مستقل عن نوع المستويات الأقل عمقا في المسند. في هذه الحالة لا يوجد عتبة الجهد. في وجود المستويات المانحة العميقة في المسند, ظاهرة backgating و بشكل مستقل عن نوع المستويات الأقل عمقا في المسند. في هذه الحالة لا يوجد عتبة الجهد. في وجود المستويات المانحة العميقة في المسند, نوع المستويات الأقل عمقا في المسند. في هذه الحالة لا يوجد عتبة الجهد. في وجود المستويات المانحة العميقة في المسند, ظاهرة backgating تتناقص مع وجود عتبة الجهد. وجود طبقة شبه ذاتية بين القناة و المسند نصف العازل يساعد أيضا في التقليل من ظاهرة backgating.

تم وضع نموذج ثنائي الأبعاد الهيدروديناميكي من أجل التنبأ بتصرف الترانزستورات ذوالتأثير الحقلي المبنية على أنصاف النواقل V-III ذات طول البوابة القصير. هذا النموذج يعتمد على معادلات الحفظ و المستنتجة من معادلات النقل لبولتزمان Boltzmann, حيث تحل في شكلها الكامل. هذا النموذج أيضا مناسب تماما لدراسة تأثير المستويات العميقة الموجودة في المسند على الترانزستور.

تمت مقارنة نتائج النموذج الهيدروديناميكي ( النموذج الفيزيائي) لتلك النتائج المتحصلة من نموذج الموزعة الكليا (النموذج الكهربائي) خاصة عند التشغيل في التواترات العالية. في الواقع, من أجل التواترات العالية, أبعاد الأقطاب للترانزستورات الميكروموجية مثل الترانزستورات ذوالتأثيرالحقلي تصبح مقاربة لطول الموجة مما يحدث تأثير التشويش للموجة المنتشرة. و لهذا, هذا التأثير يحتاج إلى تقييم دقيق في نموذج الترانزستور لضمان تصميم موثوق به.

في النموذج الكهربائي تمّ تقسيم عرض الترانزستور إلى عدد لا متناهي من القطع, في حين إعتبرنا كل قطعة من المجموعة كمساهمة ثلاث خطوط إرسال مقرونة و دائرة مكافئة للترانزستور ذوالتأثيرالحقلي كلاسيكية. لحل مجموعة المعادلات التفاضلية الناتجة, تمّ إستعمال تقنية الفروق المحدودة في المجال الزمني (FDTD) و التي تتميز بدقة زمنية و كفاءة في نمذجة الترانزستور. علاوة على ذلك, تم البرهنة على قدرة النموذج الهيدروديناميكي ثنائي الأبعاد في توفير معلومات قيّمة حول عمل الترانزستور و تم تأكيده بقياسات في حالات عدّة.

من أجل ذالك تمت دراسة تأثيرا لأبعاد التكنولوجية لترانزستور مثل طول البوابة وعمقها. وقد وجد أن تصغير طول البوابة وتعميقها يحسن من أداء الترانزستورات. وكذلك تمت دراسة تأثير زيادة كثافة دلتا-مطعمة على أداء مول البوابة وتعميقها يحسن من أداء الترانزستورات. وكذلك تمت دراسة تأثير زيادة كثافة دلتا-مطعمة على أداء مول البوابة وتعميقها يحسن من أداء الترانزستورات. وكذلك تمت دراسة تأثير زيادة كثافة دلتا-مطعمة على أداء مول البوابة وتعميقها يحسن من أداء الترانزستورات. وكذلك تمت دراسة تأثير زيادة كثافة دلتا-مطعمة على أداء مول البوابة وتعميقها يحسن من أداء الترانزستورات. وكذلك تمت دراسة تأثير زيادة كثافة دلتا-مطعمة على أداء مول البوابة وتعميقها يحسن من أداء الترانزستور ونات من طبقة AIGaAs إلى القناة InGaAs تمت كذالك دراسة تأثير المستويات العميقة في المسند، وقد وجد أن الأخذة العميقة تحسن من الأداء الترانزستور والعكس في حالة المستويات المانحة العميقة.

الكلمات الدلالية: ترانزستور تأثير حقل - ناقلية – النموذج الهيدروديناميكي - تقنية الفروق المحدودة في المجال الزمني - خطوط إرسال

#### Acknowledgment

I am highly praised and grateful to Almighty Allah, who allows me to live and accomplish tasks including the research work being presented in this thesis.

I am thankful to the following instructors who assist me throughout time and made available suggestions for the improvement of this dessirtation.

Dr. Sengouga Nouredine (Biskra University), my Ph.D. supervisor and Laboratory director of Metallic and Semiconducting Materials (LMSM), for his illustrious advice, vivid and dynamic supervision, guidance, help and patience.

He is the person, who was always there to help me during my entire graduate program and now I am very proud to have work under his supervision.

Great thank and much respect to Dr. Mustapha Cherif Eddine Yagoub Professor at School of Electrical Engineering and Computer Science (SEECS), University of Ottawa (Canada), who supported me all the time near and far. I offer my sincerest gratitude to his person for his interests, encouragement, good advices, most co-operative, confident and constructive thoughtful, which have positive aspects in the completion of this thesis.

I would like to thank deeply Dr. Afak. Meftah for her acceptance to be the president of the jury and it is a great honour for me. My thanks are also given to Dr. Dehimi Lakhdar, Dr. Ledra Mohammed and Dr. Hemaizia Zahra for their acceptance to be members of the examination committee.

I would like also to take the chance to thank the Administration staf for providing me a suitable atmosphere to facilitate the research work, among them Dr. Chala Abdelwahed the vice president, Dr. Attaf Abedellah the vice dean of the faculty of Exact Sciences and Sciences of nature and life and Dr Mezerdi Brahim Vice Rector in charge of External Relations, Cooperation, entertainment and communication and Scientific Events of Biskra's University.

I would like to express my feeling of gratitude **to my parents** who prayed for my health and successful future, my sisters and brothers for their love and encouragement, which has enabled me to finish this dissertation.

Thanks so much to my friends: Ksiret Fouzya, Tigrine Zahia, Lehrak Nadia, Djouama Torkia, Guerguet Aicha, Chikhaoui Selma, Aissaoui Fatiha, Chahri Abdellah, Soufi Yassine, Hezabra Adel, Tibermacine Toufik and to all my special LMSM collegues. In fact, I would not have reached my aim without their sincere love and support. I dedicate this work to my loved Father, my Praiseworthy two mothers, to the nicest person Boussaha Abdeldjalil (late), to Dr Sengouga Nouredine for his support and assistance and to Dr Mustapha Cherif-Eddine Yagoub for guiding me with respect and patience.

## **Table of Contents**

| Abstract      |                                                  | i     |

|---------------|--------------------------------------------------|-------|

| Résumé        |                                                  | ii    |

| ملخص          |                                                  | iii   |

| Acknowledg    | gement                                           | V     |

| Dedication    | -                                                | vi    |

| Table of Co   | ntents                                           | vii   |

| List of Figu  |                                                  | xi    |

| List of Table |                                                  | XV    |

| List of Acro  |                                                  | xvii  |

| List of Syml  |                                                  | xviii |

| Introduction  |                                                  | 1     |

|               | vation                                           | 1     |

|               | ribution overview                                | 3     |

|               | is Outline                                       | 4     |

| Chapter I     | Field Effect Transistors                         | 5     |

| -             | troduction                                       | 5     |

|               | roperties of Material for MESFETs and HEMTs      | 6     |

| 1.211         | I.2.1 GaAs Material                              | 6     |

|               | I.2.2 $Al_xGa_{1-x}As$ alloys                    | 7     |

|               | I.2.3 $In_{1-x}Ga_xAs_yP_{1-y}$ alloys           | 8     |

| I.3 TI        | he GaAs MESFET technology                        | 9     |

|               | aAs MESFET operation                             | 11    |

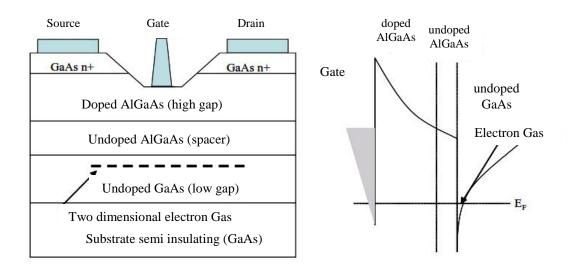

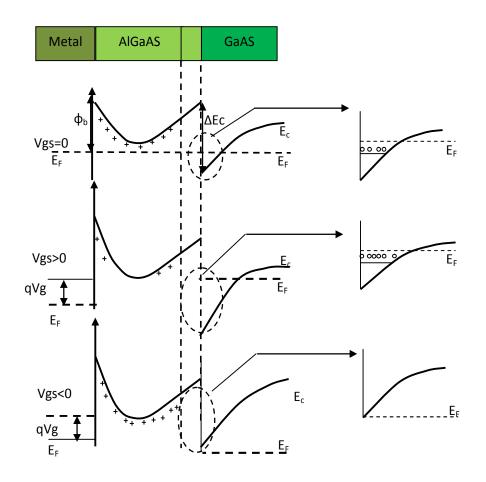

| I.5 H         | igh electron mobility transistors                | 13    |

|               | I.5.1 Introduction                               | 13    |

|               | I.5.2.1 Analytical description of HEMT operation | 14    |

|               | I.5.2.1 Linear charge control model              | 14    |

|               | I.5.2.2 Modulation efficiency                    | 16    |

|               | I.5.2.3 Current-voltage (I-V) models for HEMT    | 17    |

|               | I.5.3 .3 Material systems for HEMTs              | 18    |

|               | I.5.3.1 AlGaAs/(In)GaAs/GaAs (GaAs pHEMT)        | 22    |

| I.6 C         | omparative study of HEMT, pHEMT and MESFET       | 23    |

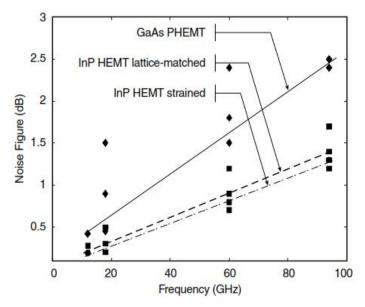

|               | I.6.1 Low-noise applications                     | 24    |

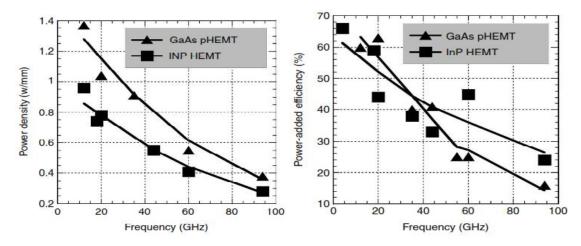

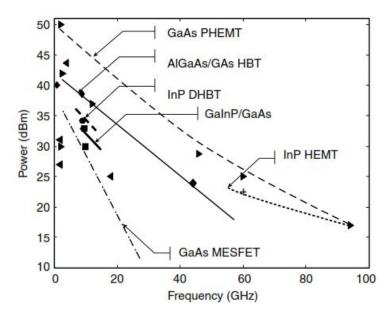

|               | I.6.2 Microwave Power Applications               | 26    |

| I.7 Su        | ummary                                           | 28    |

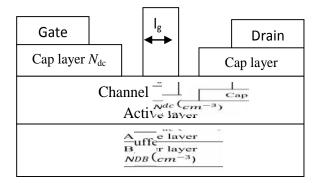

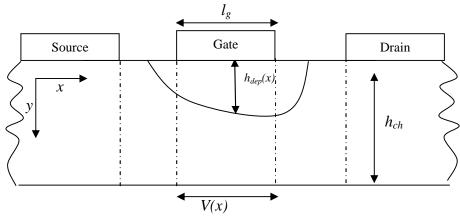

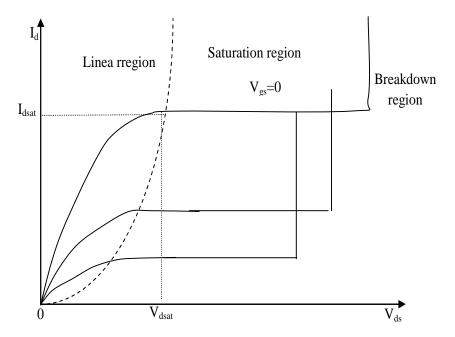

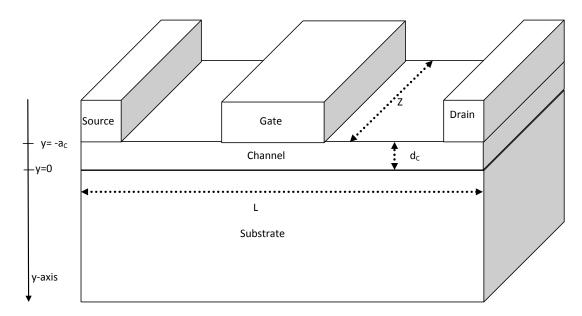

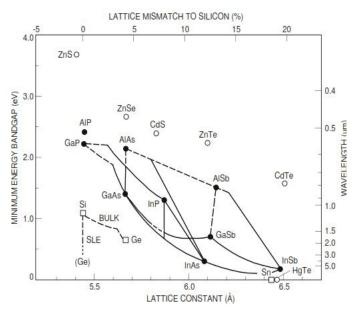

| II.1 Introduction29II.2 Two Dimensional Hydrodynamic FET Model30II.2 Two Dimensional Hydrodynamic FET Model30II.2.2 Poisson' equation31II.2.2 Devison' equations33II.2.4 Hydrodynamic transport equations33II.2.5 Carrier mobility35II.2.5 Larrier mobility36II.2.5 Larrier mobility36II.2.5 Larrier mobility36II.2.5 Larrier mobility36II.2.5 Degative differential mobility36II.2.6 Boundary physics36II.2.7 Numerical solution procedures37II.2.7.1 Meshes38II.2.7.2 Newton method39II.2.7.3 The current driven DC I-V simulation39II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs46II.4.2 The deep level in HEMTs46II.4.2 The May center model47II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect Transistors51III.2 Intervise description52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2 Physical meaning of the circuit elements57III.2.2 Physical meaning of the circuit elements57III.2.2 Physical meaning of the circuit clements57III.2.2.3 Parasitic regacitances C <sub>18</sub> and C <sub>14</sub> 58III.2.2.4 Parasitic capacitances C <sub>18</sub> and C <sub>14</sub>                                                                      | Chapter II  | Physical Modelling of Field Effect Transistors                               | 29 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|------------------------------------------------------------------------------|----|

| II.2.1 Model description       30         II.2.2 Poisson' equation       31         II.2.3 Carrier statistics       31         II.2.4 Hydrodynamic transport equations       33         II.2.5 Carrier mobility       35         II.2.5.1 Standard field-dependent mobility       35         II.2.5.2 Negative differential mobility       36         II.2.5.1 Standard field-dependent mobility       36         II.2.5.2 Negative differential mobility       36         II.2.7.1 Meshes       38         II.2.7.2 Newton method       39         II.3.1 Model Description       40         II.3.2 Numerical resolution       42         II.4 Deep level effects on GaAs MESFETs and HEMTs       43         II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide       44         II.4.2.1 The DX center model       47         II.4.2 The substrate trap model       48         II.4.2 The substrate trap model       48         II.4.3 Backgating effect       49         II.5 Summary       50         Chapter III Analytical and Electrical Modelling of Field Effect Transistors       51         III.2 The WESFET       52         III.2.1 Device description       52         III.2.2.2 Parasitic resistances R <sub>a</sub> R <sub>a</sub> a                                      | II.1 Iı     | ntroduction                                                                  | 29 |

| II.2.2 Poisson' equation       31         II.2.3 Carrier statistics       31         II.2.4 Hydrodynamic transport equations       33         II.2.5 Carrier mobility       35         II.2.5.1 Standard field-dependent mobility       36         II.2.5.2 Negative differential mobility       36         II.2.6 Boundary physics       36         II.2.7 Numerical solution procedures       37         II.2.7.1 Meshes       38         II.2.7.2 Newton method       39         II.2.7.3 The current driven DC I-V simulation       39         II.3.1 Model Description       40         II.3.2 Numerical resolution       42         II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide       44         II.4.2.1 The DX center model       47         II.4.2.1 The DX center model       47         II.4.2.2 The substrate trap model       48         II.4.2.1 The DX center model       47         II.4.2.2 The substrate trap model       48         II.4.2.3 Backgating effect       49         II.5 Summary       50         Chapter III       Analytical and Electrical Modelling of Field Effect Transistors       51         III.1 Introduction       51         III.2.2 Physical meaning of the circuit                                                                    | II.2 T      | wo Dimensional Hydrodynamic FET Model                                        | 30 |

| II.2.3 Carrier statistics31II.2.4 Hydrodynamic transport equations33II.2.5 Carrier mobility35II.2.5.1 Standard field-dependent mobility35II.2.5.2 Negative differential mobility36II.2.6 Boundary physics36II.2.7 Numerical solution procedures37II.2.7.1 Meshes38II.2.7.2 Newton method39II.2.7.3 The current driven DC I-V simulation39II.3 The drift diffusion model40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTS43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The data deep level in HEMTS46II.4.2.1 The DX center model47II.4.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect Transistors51III.1 Introduction52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2.3 Parasitic resistances R <sub>0</sub> , R <sub>4</sub> and R <sub>8</sub> 58III.2.2.4 Parasitic capacitances C <sub>05</sub> and C <sub>pt</sub> 58III.2.3 Parasitic capacitances C <sub>05</sub> and C <sub>pt</sub> 58III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60             |             | II.2.1 Model description                                                     | 30 |

| II.2.4 Hydrodynamic transport equations33II.2.5 Carrier mobility35II.2.5.1 Standard field-dependent mobility35II.2.5.2 Negative differential mobility36II.2.6 Boundary physics36II.2.7 Numerical solution procedures37II.2.7.1 Meshes38II.2.7.2 Newton method39II.2.7.3 The current driven DC I-V simulation39II.3.1 Model Description40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2 The deep level in HEMTs46II.4.2 The substrate trap model47II.4.2 The substrate trap model48II.4.3 Backgating effect49II.2 The MESFET51III.1 Introduction51III.2 Device description51III.2 Device description52III.2.1 Device description52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2.3 Parasitic resistances R <sub>19</sub> and Is,<br>III.2.2.3 Parasitic resistances R <sub>19</sub> and R <sub>4</sub> 58III.2.2.4 Parasitic capacitances C <sub>195</sub> and C <sub>196</sub> 58III.2.2.5 Cut-off frequency59III.3.1 Introduction60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaASFET Small-signal model60 <td></td> <td>II.2.2 Poisson' equation</td> <td>31</td> |             | II.2.2 Poisson' equation                                                     | 31 |

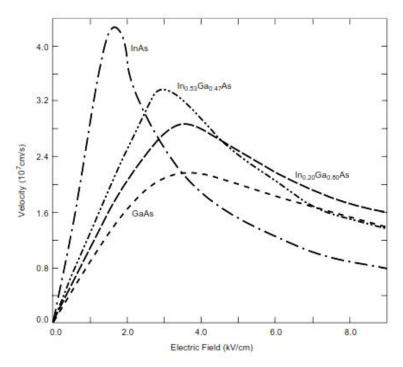

| II.2.5 Carrier mobility35II.2.5.1 Standard field-dependent mobility35II.2.5.2 Negative differential mobility36II.2.5.2 Negative differential mobility36II.2.7.1 Numerical solution procedures37II.2.7.1 Meshes38II.2.7.2 Newton method39II.3.7 be drift diffusion model40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2 The duep level in HEMTs46II.4.2 The substrate trap model47II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect Transistors51III.2 The MESFET52III.2 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2.1 Drivice description52III.2.2.2 Prastitic inductances $L_g$ Lq and $L_g$ 58III.2.2.3 Parasitic resistances $R_{ng}$ and $C_{pd}$ 58III.2.2.4 Parasitic capacitances $C_{ng}$ and $C_{pd}$ 58III.2.2.5 Cut-off frequency59III.3 Introduction60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                         |             | II.2.3 Carrier statistics                                                    | 31 |

| II.2.5.1 Standard field-dependent mobility35II.2.5.2 Negative differential mobility36II.2.5.2 Negative differential mobility36II.2.7 Numerical solution procedures37II.2.7.1 Meshes38II.2.7.2 Newton method39II.2.7.3 The current driven DC I-V simulation39II.3 The drift diffusion model40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2 The duep level in HEMTs46II.4.2 The substrate trap model47II.4.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect Transistors51III.2 Device description52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2 Physical meaning of the circuit elements57III.2.2 Physical meaning of the circuit elements57III.2.2.3 Parasitic resistances Ray Ray and Ray58III.2.2.4 Parasitic capacitances Cirg and Cirel59III.3 Small-signal model60III.3.1 Introduction60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                           |             | II.2.4 Hydrodynamic transport equations                                      | 33 |

| II.2.5.2 Negative differential mobility36II.2.6 Boundary physics36II.2.7 Numerical solution procedures37II.2.7.1 Meshes38II.2.7.2 Newton method39II.2.7.3 The current driven DC I-V simulation39II.3 The drift diffusion model40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect Transistors51III.2.1 Device description52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2.3 Parasitic inductances L <sub>12</sub> , L <sub>4</sub> and L <sub>8</sub> 58III.2.2.4 Parasitic inductances L <sub>12</sub> , L <sub>4</sub> and L <sub>8</sub> 58III.2.2.5 Cut-off frequency59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                         |             | II.2.5 Carrier mobility                                                      | 35 |

| II.2.6 Boundary physics       36         II.2.7 Numerical solution procedures       37         II.2.7.1 Meshes       38         II.2.7.2 Newton method       39         II.2.7.3 The current driven DC I-V simulation       39         II.3 The drift diffusion model       40         II.3.1 Model Description       40         II.3.2 Numerical resolution       42         II.4 Deep level effects on GaAs MESFETs and HEMTs       43         II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide       44         II.4.2 The deep level in HEMTs       46         II.4.2.1 The DX center model       47         II.4.2.2 The substrate trap model       48         II.4.3 Backgating effect       49         IJ.5 Summary       50         Chapter III       Analytical and Electrical Modelling of Field Effect Transistors       51         III.2 The MESFET       52         III.2.1 Device description       52         III.2.2 Physical meaning of the circuit elements       54         III.2.2.3 Parasitic resistances R <sub>s</sub> , R <sub>d</sub> and R <sub>g</sub> 58         III.2.2.4 Parasitic capacitances C <sub>sp</sub> and C <sub>pd</sub> 58         III.2.2.5 Cut-off frequency       59         III.3.1 Introduction       60                                 |             | II.2.5.1 Standard field-dependent mobility                                   | 35 |

| II.2.7 Numerical solution procedures37II.2.7.1 Meshes38II.2.7.2 Newton method39II.2.7.3 The current driven DC I-V simulation39II.3 The drift diffusion model40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect TransistorsIII.2 The MESFET52III.2.1 Device description51III.2.2 Physical meaning of the circuit elements57III.2.2 Physical meaning of the circuit elements57III.2.2 Physical meaning of the circuit elements57III.2.2.1 Service description52III.2.2 Physical meaning of the circuit elements57III.2.2 Physical meaning of the circuit elements57III.2.2 Physical capacitances $C_{pg}$ and $C_{pd}$ 58III.2.2.4 Parasitic capacitances $C_{pg}$ and $C_{pd}$ 58III.2.2.5 Cut-off frequency59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                             |             | II.2.5.2 Negative differential mobility                                      | 36 |

| II.2.7.1 Meshes38II.2.7.2 Newton method39II.2.7.3 The current driven DC I-V simulation39II.3 The drift diffusion model40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter IIIAnalytical and Electrical Modelling of Field Effect Transistors51III.2 The MESFET52III.2.1 Device description51III.2.2 Physical meaning of the circuit elements57III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic resistances R <sub>x</sub> , R <sub>d</sub> and R <sub>g</sub> 58III.2.2.4 Parasitic capacitances C <sub>pg</sub> and C <sub>pd</sub> 58III.2.2.5 Cut-off frequency59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                              |             | II.2.6 Boundary physics                                                      | 36 |

| II.2.7.2 Newton method       39         II.2.7.3 The current driven DC I-V simulation       39         II.3 The drift diffusion model       40         II.3.1 Model Description       40         II.3.2 Numerical resolution       42         II.4 Deep level effects on GaAs MESFETs and HEMTs       43         II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide       44         II.4.2 The deep level in HEMTs       46         II.4.2.1 The DX center model       47         II.4.3 Backgating effect       49         II.5 Summary       50         Chapter III Analytical and Electrical Modelling of Field Effect Transistors       51         III.2 The MESFET       52         III.2.1 Device description       52         III.2.2 Physical meaning of the circuit elements       54         III.2.2.1 Intrinsic elements       57         III.2.2.2 Parasitic resistances R <sub>18</sub> d and R <sub>2</sub> 58         III.2.2.4 Parasitic capacitances C <sub>pg</sub> and C <sub>pd</sub> 58         III.2.2.5 Cut-off frequency       59         III.3.1 Introduction       60         III.3.1 Introduction       60         III.3.1 Introduction       60         III.3.2 Parameter extraction technologies for GaAsFET Small-signal model       60                    |             | II.2.7 Numerical solution procedures                                         | 37 |

| II.2.7.3 The current driven DC I-V simulation39II.3 The drift diffusion model40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect TransistorsIII.1 Introduction51III.2.1 Device description52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2.1 Intrinsic elements57III.2.2.2 Prastic inductances Lg, Ld and Lg58III.2.2.3 Parastic resistances R_g, R_d and Rg58III.2.2.5 Cut-off frequency59III.3.2 Small-signal model60III.3.1 Introduction60III.3.2 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                 |             | II.2.7.1 Meshes                                                              | 38 |

| II.3 The drift diffusion model40II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.2.1 The DX center model49II.4.3 Backgating effect49II.5 Summary50Chapter IIIAnalytical and Electrical Modelling of Field Effect Transistors51III.2 The MESFET52III.2.1 Device description51III.2.2 Physical meaning of the circuit elements57III.2.2.1 Intrinsic elements57III.2.2.2 Prasitic inductances Lg, Ld and Lg58III.2.2.5 Cut-off frequency59III.2.3.5 Cut-off frequency59III.3.5 mall-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | II.2.7.2 Newton method                                                       | 39 |

| II.3.1 Model Description40II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter IIIAnalytical and Electrical Modelling of Field Effect Transistors51III.2 The MESFET52III.2.1 Device description51III.2.2 Physical meaning of the circuit elements54III.2.2.2 Parasitic inductances L <sub>g</sub> L <sub>d</sub> and L <sub>s</sub> 57III.2.2.3 Parasitic resistances R <sub>s</sub> , R <sub>d</sub> and R <sub>g</sub> 58III.2.2.4 Parasitic capacitances C <sub>pg</sub> and C <sub>pd</sub> 59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                              |             | II.2.7.3 The current driven DC I-V simulation                                | 39 |

| II.3.2 Numerical resolution42II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect TransistorsII.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances L <sub>g</sub> , L <sub>d</sub> and L <sub>s</sub> 57III.2.2.3 Parasitic resistances R <sub>s</sub> , R <sub>d</sub> and R <sub>g</sub> 58III.2.2.4 Parasitic capacitances C <sub>Pg</sub> and C <sub>pd</sub> 58III.2.2.5 Cut-off frequency59III.3.1 Introduction60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                             | II.3 T      | he drift diffusion model                                                     | 40 |

| II.4 Deep level effects on GaAs MESFETs and HEMTs43II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect TransistorsIII.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | II.3.1 Model Description                                                     | 40 |

| II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide44II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect TransistorsIII.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements54III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic capacitances Cpg and Cpd58III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | II.3.2 Numerical resolution                                                  | 42 |

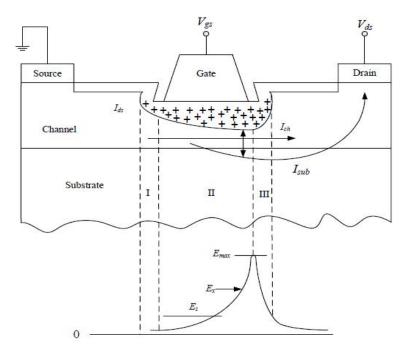

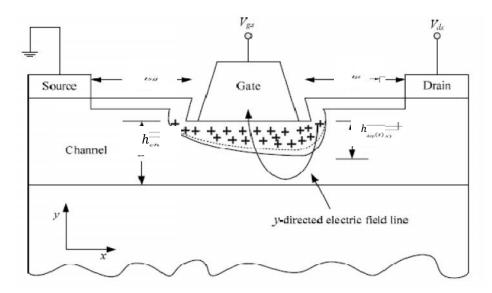

| II.4.2 The deep level in HEMTs46II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect TransistorsIII.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2.1 Intrinsic elements54III.2.2.2 Physical meaning of the circuit elements57III.2.2.3 Parasitic resistances Lg, Ld and Lg57III.2.2.4 Parasitic capacitances Cg and Cgd58III.2.2.5 Cut-off frequency59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | II.4 D      | eep level effects on GaAs MESFETs and HEMTs                                  | 43 |

| II.4.2.1 The DX center model47II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect TransistorsIII.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements57III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic resistances R <sub>s</sub> , R <sub>d</sub> and R <sub>g</sub> 58III.2.2.4 Parasitic capacitances C <sub>pg</sub> and C <sub>pd</sub> 58III.2.2.5 Cut-off frequency59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | II.4.1 The Nature of deep denters in different varieties of Gallium-Arsenide | 44 |

| II.4.2.2 The substrate trap model48II.4.3 Backgating effect49II.5 Summary50Chapter IIIAnalytical and Electrical Modelling of Field Effect Transistors51III.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements54III.2.2.1 Intrinsic elements57III.2.2.3 Parasitic resistances R <sub>s</sub> , R <sub>d</sub> and R <sub>g</sub> 58III.2.2.4 Parasitic capacitances C <sub>pg</sub> and C <sub>pd</sub> 58II.2.2.5 Cut-off frequency59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |             | II.4.2 The deep level in HEMTs                                               | 46 |

| II.4.3 Backgating effect49II.5 Summary50Chapter III Analytical and Electrical Modelling of Field Effect Transistors51III.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements54III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.5 Cut-off frequency59III.3.5 mall-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |             | II.4.2.1 The DX center model                                                 | 47 |

| II.5 Summary50Chapter IIIAnalytical and Electrical Modelling of Field Effect Transistors51III.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements54III.2.2 Physical meaning of the circuit elements57III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | II.4.2.2 The substrate trap model                                            | 48 |

| Chapter IIIAnalytical and Electrical Modelling of Field Effect Transistors51III.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements54III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | II.4.3 Backgating effect                                                     | 49 |

| III.1 Introduction51III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements54III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | II.5 S      | ummary                                                                       | 50 |

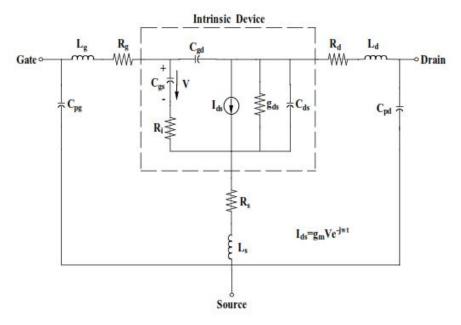

| III.2 The MESFET52III.2.1 Device description52III.2.2 Physical meaning of the circuit elements54III.2.2 Physical meaning of the circuit elements57III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Chapter III | Analytical and Electrical Modelling of Field Effect Transistors              | 51 |

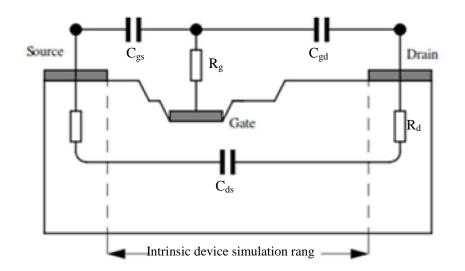

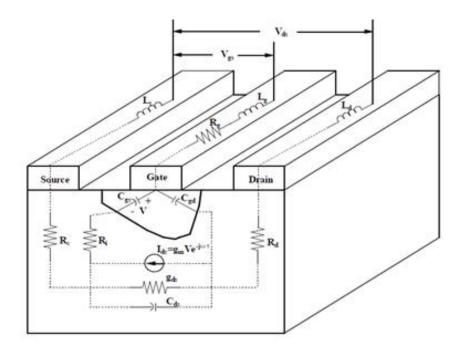

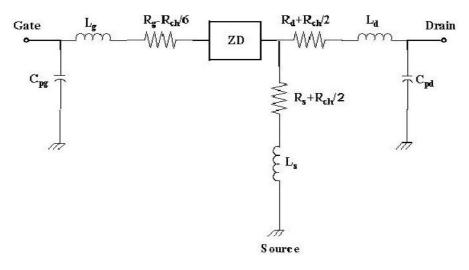

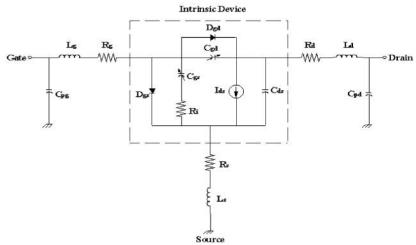

| III.2.1 Device description52III.2.2 Physical meaning of the circuit elements54III.2.2 Physical meaning of the circuit elements57III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | III.1 I     | ntroduction                                                                  | 51 |

| III.2.2 Physical meaning of the circuit elements54III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | III.2       | The MESFET                                                                   | 52 |

| III.2.2.1 Intrinsic elements57III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | III.2.1 Device description                                                   | 52 |

| III.2.2.2 Parasitic inductances Lg, Ld and Ls57III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |             | III.2.2 Physical meaning of the circuit elements                             | 54 |

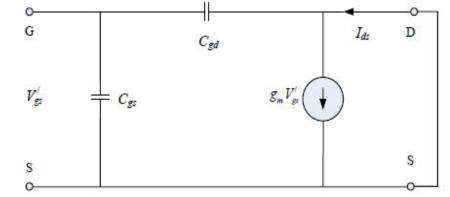

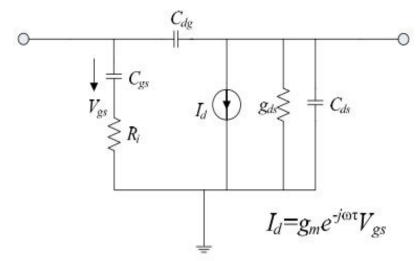

| III.2.2.3 Parasitic resistances Rs, Rd and Rg58III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |             | III.2.2.1 Intrinsic elements                                                 | 57 |

| III.2.2.4 Parasitic capacitances Cpg and Cpd58III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |             | III.2.2.2 Parasitic inductances $L_g$ , $L_d$ and $L_s$                      | 57 |

| III.2.2.5 Cut-off frequency59III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |             | III.2.2.3 Parasitic resistances $R_s$ , $R_d$ and $R_g$                      | 58 |

| III.2.2.6 Transconductance delay59III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |             | III.2.2.4 Parasitic capacitances $C_{pg}$ and $C_{pd}$                       | 58 |

| III.3 Small-signal model60III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             | III.2.2.5 Cut-off frequency                                                  | 59 |

| III.3.1 Introduction60III.3.2 Parameter extraction technologies for GaAsFET Small-signal model60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |             | III.2.2.6 Transconductance delay                                             | 59 |

| III.3.2 Parameter extraction technologies for GaAsFET Small-signal model 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | III.3 S     | Small-signal model                                                           | 60 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | III.3.1 Introduction                                                         | 60 |

| III.3.2.1 De-embedding technique 60                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |             | III.3.2 Parameter extraction technologies for GaAsFET Small-signal model     | 60 |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |             | III.3.2.1 De-embedding technique                                             | 60 |

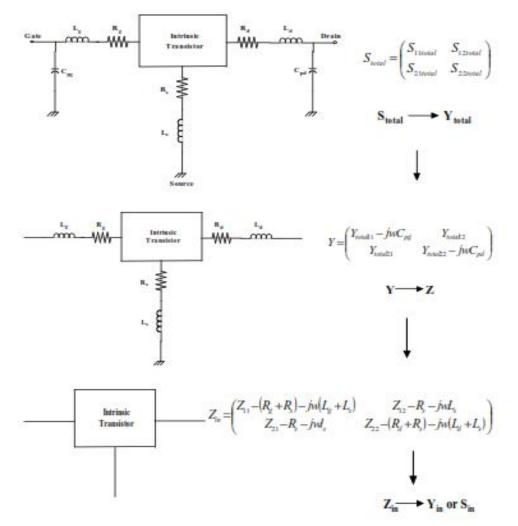

|            | III.3.2.2 De-embedding procedure of typical FET device parasitic |     | 61  |

|------------|------------------------------------------------------------------|-----|-----|

|            | III.3.3 Cold-FET Techniques                                      |     | 62  |

|            | III.3.3.1 Extraction of parasitic resistances and inductances    |     | 62  |

|            | III.3.4 Hot-FET Techniques                                       |     | 65  |

| III.4 N    | IESFET Nonlinear properties: Large-signal models                 |     | 66  |

| III.5 N    | onlinear transistor models                                       |     | 67  |

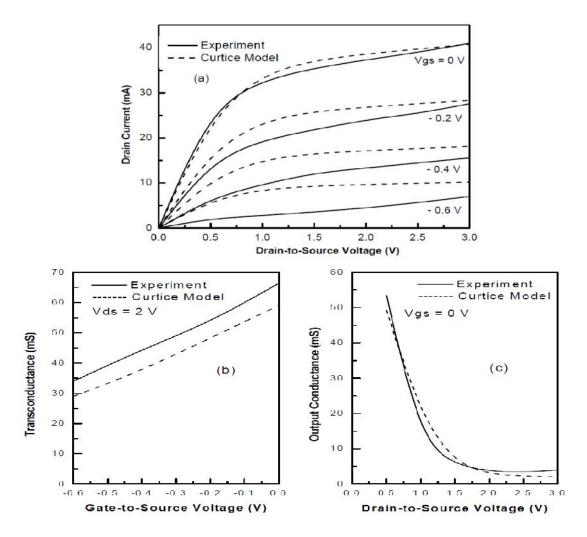

|            | III.5.1 Curtice quadratic model                                  |     | 67  |

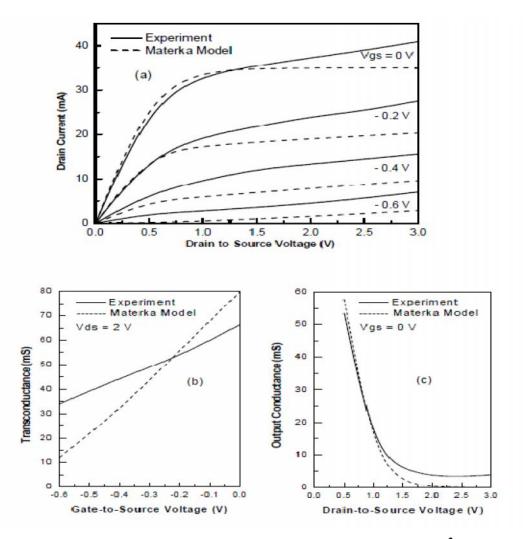

|            | III.5.2 Materka model                                            |     | 68  |

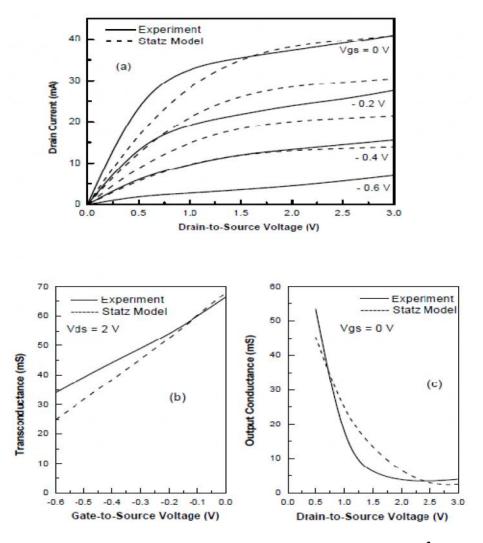

|            | III.5.3 Statz model                                              |     | 70  |

|            | III.5.4 Curtice Ettenberg Cubic model                            |     | 72  |

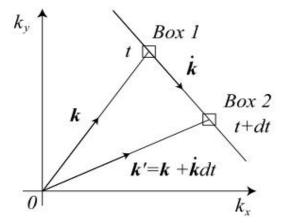

| III.6 F    | inite Differential Time Domain Analysis (FDTD)                   |     | 74  |

|            | III.6.1 Introduction                                             |     | 74  |

|            | III.6.2 Model Identification                                     |     | 75  |

|            | III.6.2.1 Solution of the linear system                          |     | 78  |

| III.7 S    | ummary                                                           |     | 80  |

| Chapter IV | Results and discussions                                          |     | 81  |

| IV.1 Ir    | ntroduction                                                      |     | 81  |

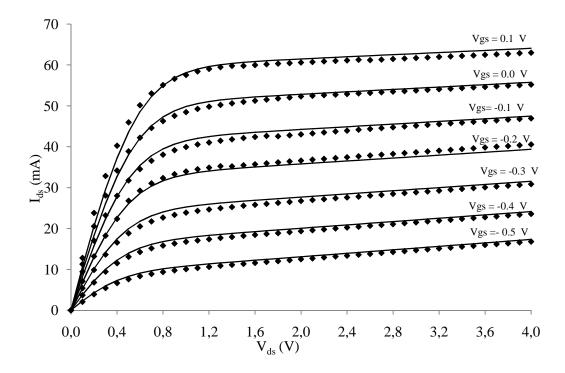

| IV.2 P     | lanar GaAs MESFET                                                |     | 82  |

|            | IV.2.1. Introduction                                             |     | 82  |

|            | IV.2.2. Sample structure                                         |     | 82  |

|            | IV.2.5 Backgating effect                                         |     | 83  |

|            | IV.2.6 Simulation results                                        |     | 84  |

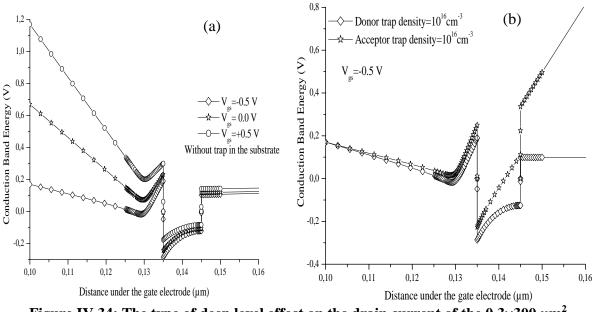

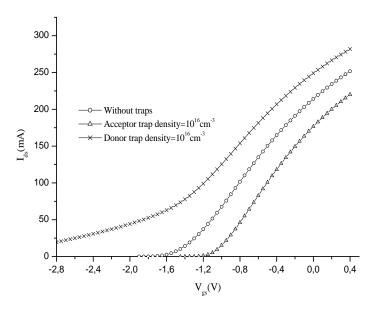

|            | IV.2.6.1 The effect of deep acceptors and donors                 |     | 84  |

|            | IV.2.6.2 The presence of a buffer layer                          |     | 85  |

|            | IV.2.7 Conclusion                                                |     | 87  |

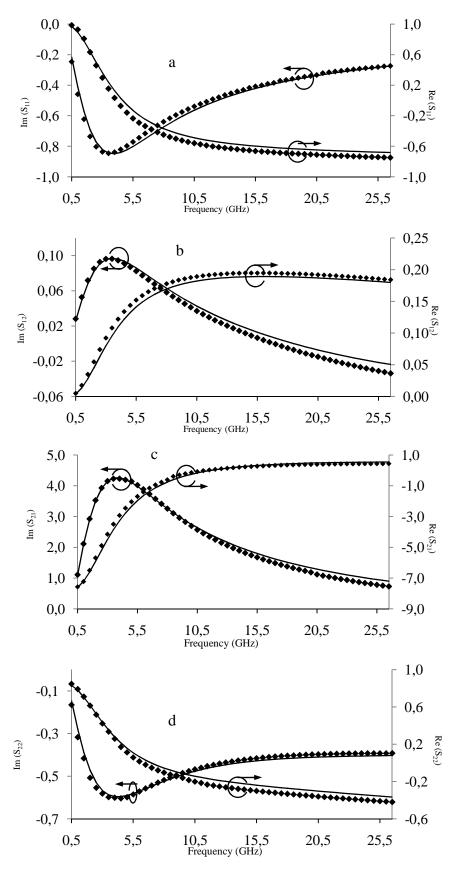

| IV.3 R     | ecessed gate GaAs MESFET                                         |     | 87  |

|            | IV.3.1 Introduction                                              |     | 87  |

|            | IV.3.2 The hydrodynamic model                                    |     | 87  |

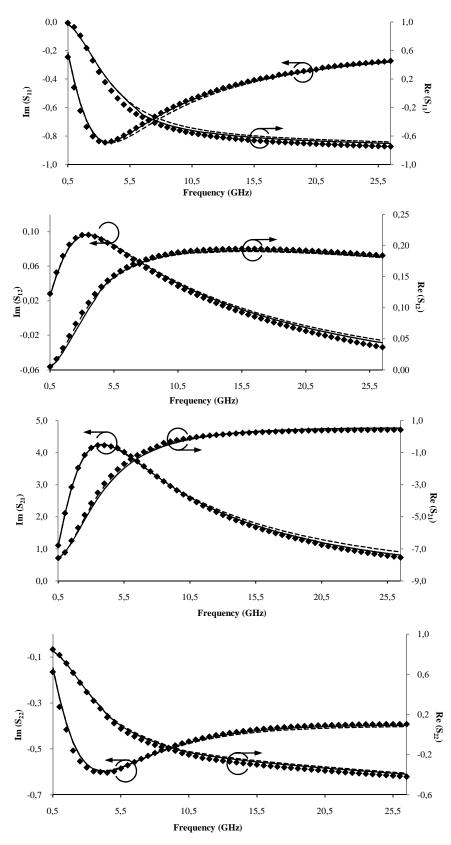

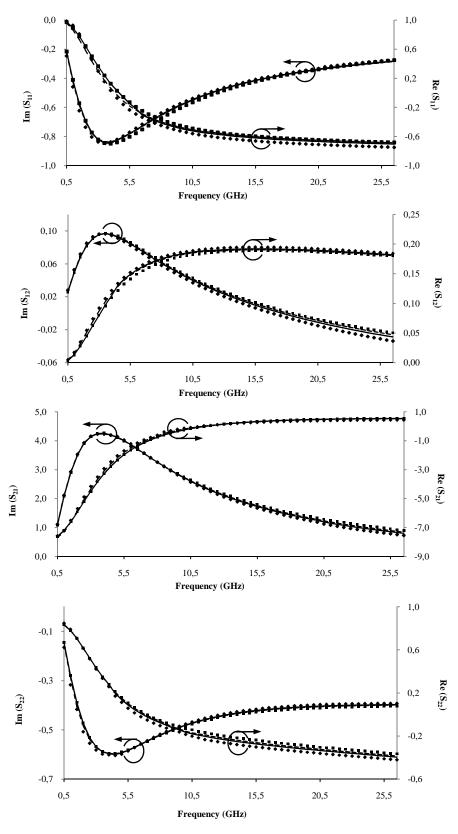

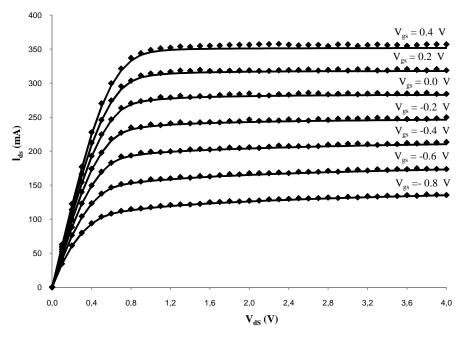

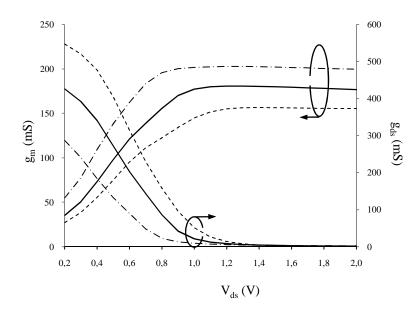

|            | IV.3.3 Electrical modelling                                      |     | 91  |

|            | IV.3.4 Comparison between HDM and ADS                            |     | 95  |

|            | IV.3.5 Effect of the gate length                                 |     | 99  |

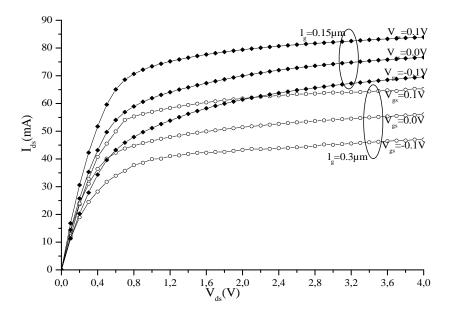

|            | IV.3.5.1 Effect of the gate length on the I-V characteristics    |     | 99  |

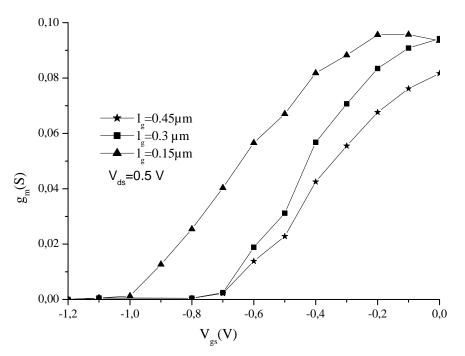

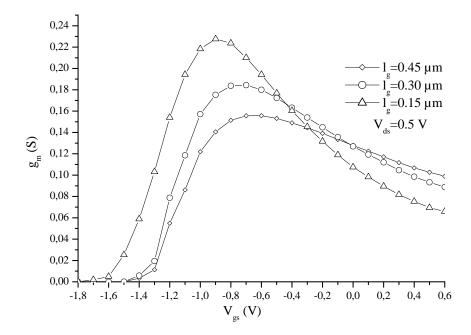

|            | IV.3.5.2 Effect of the gate length on the transconductance       |     | 100 |

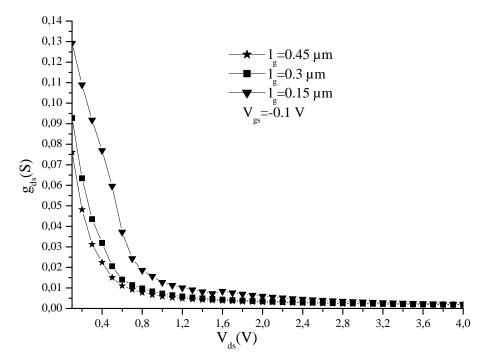

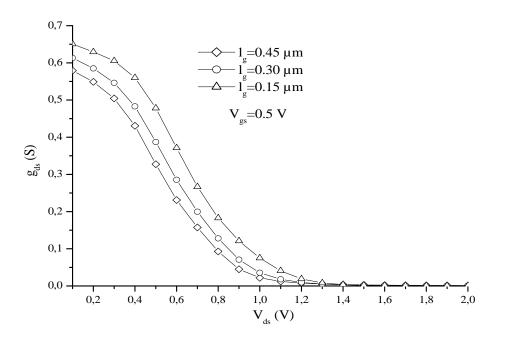

|            | IV.3.5.3 Effect of the gate length on the output conductance     |     | 100 |

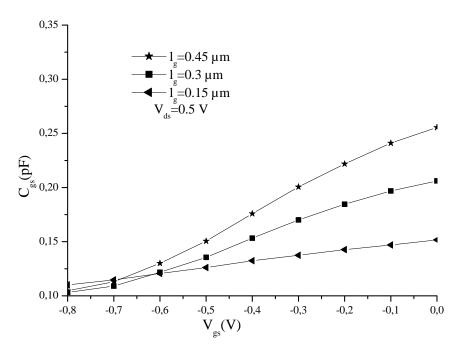

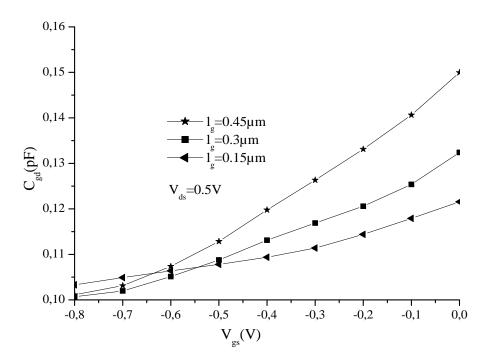

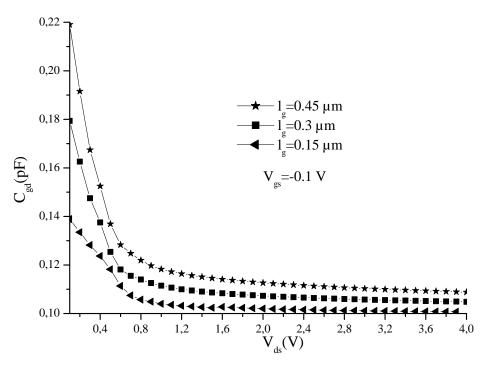

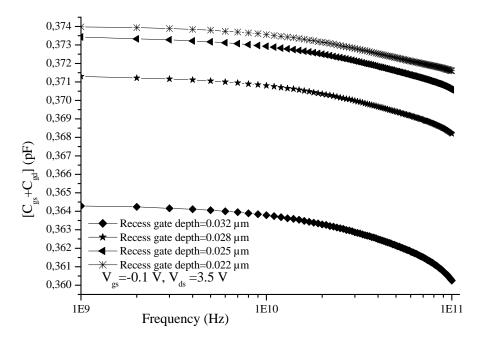

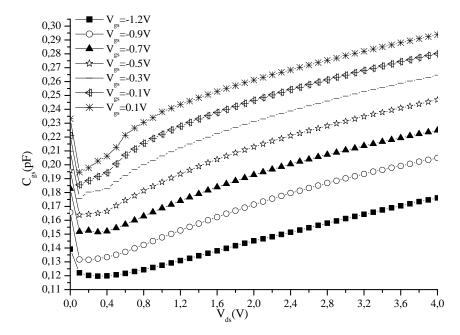

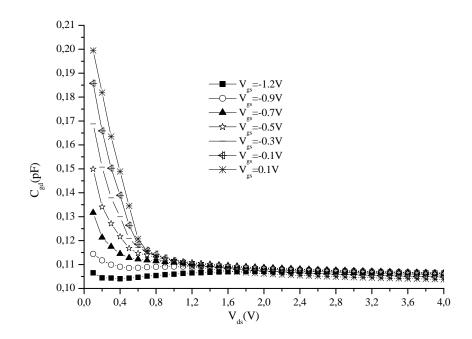

|            | IV.3.5.4 Effect of the gate length on the capacitances           | 101 |     |

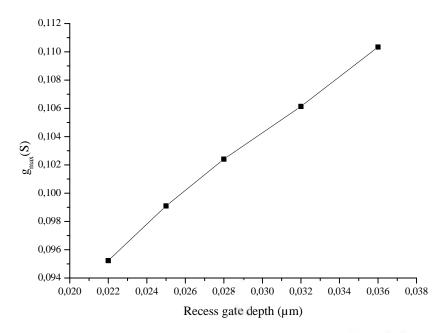

|            | IV.3.6 Effect of recess gate depth                               |     | 104 |

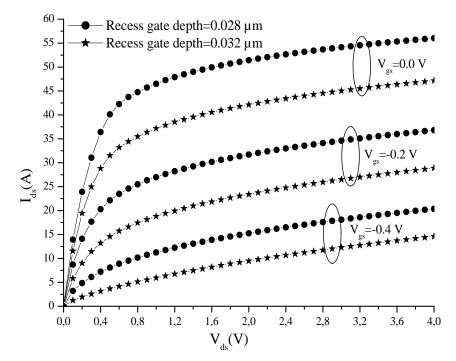

|            | IV.3.6.1 Effect of recess gate depth on the I-V characteristics  |     | 104 |

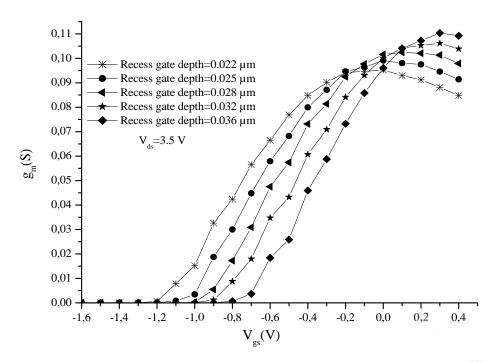

|            | IV.3.6.2 Effect of recess gate depth on the transconductance     |     | 105 |

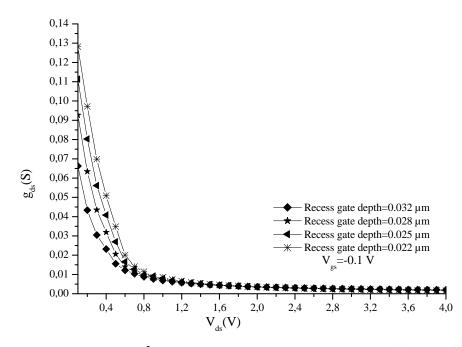

|            | IV.3.6.3 Effect of recess gate depth on the output condcutance   |     | 107 |

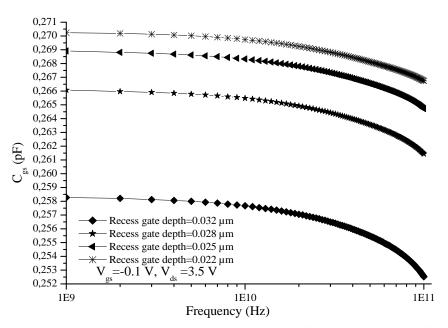

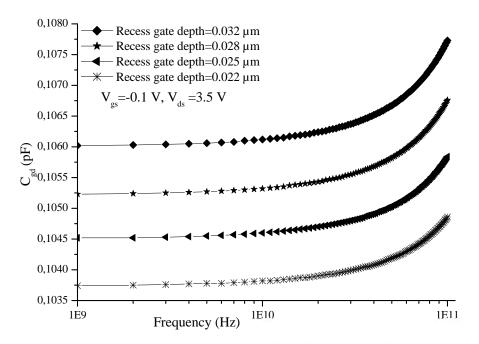

|            | IV.3.6.4 Effect of recess gate depth on the capacitances         |     | 107 |

|               | IV.3.7 Nonlinear-regime capacitance                         | 109 |

|---------------|-------------------------------------------------------------|-----|

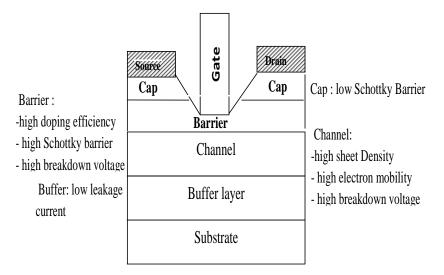

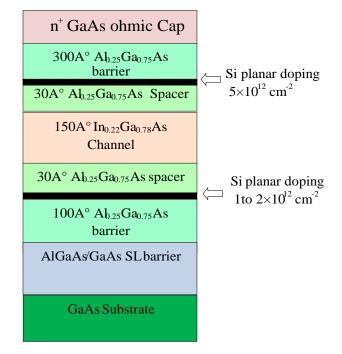

| IV.4 Th       | ne AlGaAs/InGaAs/GaAs pseudomorphic high electron           |     |

| 1             | mobility transistor (pHEMT)                                 | 112 |

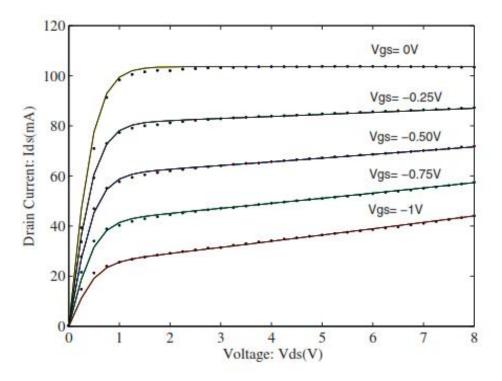

|               | IV.4.1 The I-V characteristics for AlGaAs/InGaAs/GaAs pHEMT | 112 |

|               | IV.4.2 The transconductance-voltage dependence of           |     |

|               | the AlGaAs/InGaAs/GaAs pHEMT                                | 113 |

|               | IV.4.3 The output conductance-voltage dependence of the     |     |

|               | AlGaAs/InGaAs/GaAs pHEMT                                    | 114 |

|               | IV.4.4 The delta doping dependence of the                   |     |

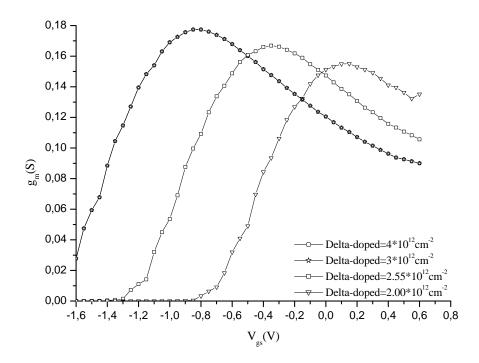

|               | AlGaAs/InGaAs/GaAs pHEMT                                    | 115 |

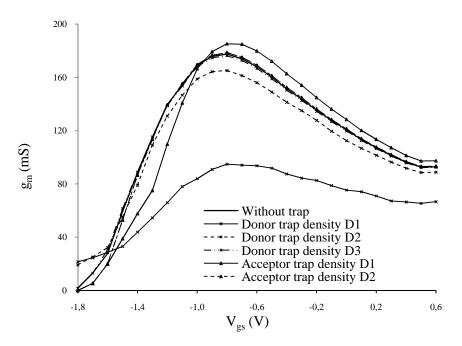

|               | IV.4.5 Trapping effect on the HEMTs element parameters      | 116 |

|               | IV.5 Summary                                                | 118 |

| Conclusion an | nd Future Work                                              | 122 |

| Appendix A:   | Helpful definitions                                         | 124 |

| A.I. Int      | roduction                                                   | 124 |

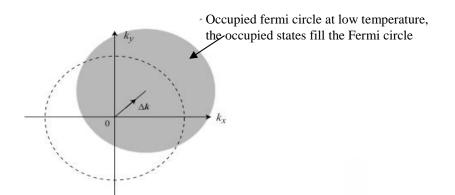

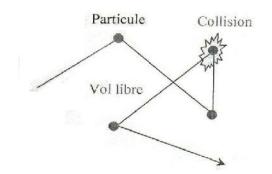

| A.II. So      | ome helpful electron transport model definitions            | 126 |

| A. II.1       | Boltzmann's transport equation:                             | 126 |

| A.II.2 7      | The drift diffusion model                                   | 130 |

| A.II.3 I      | Deriving hydrodynamic equations from the Boltzmann equation | 133 |

| A.III M       | Ionte Carlo Method                                          | 135 |

| Appendix B:   | Defining terms                                              | 138 |

| References    |                                                             | 147 |

# List of Figures

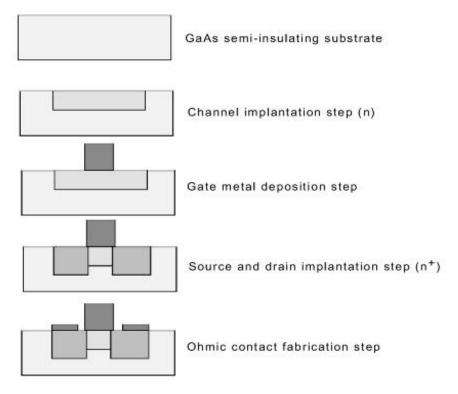

| Figure I.1: Fabrication steps for self-aligned GaAs MESFET                               |    |

|------------------------------------------------------------------------------------------|----|

| [Higgins et al; 1978, Welch and Eden; 1977].                                             | 10 |

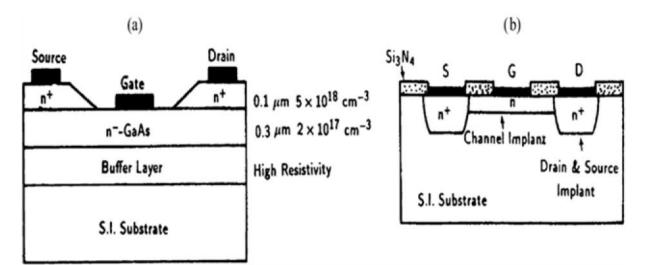

| Figure I.2:Two widespeared GaAs MESFET methods (a) epitaxial                             |    |

| and (b) ion implantation [Sheng; 2006].                                                  | 12 |

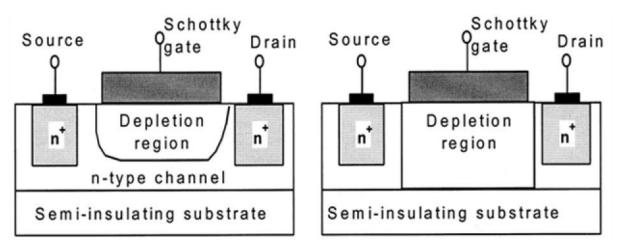

| Figure I.3: Normally-on (a) and normally-off (b) MESFETs at                              |    |

| zero gate bias [Yasuto; 2012].                                                           | 13 |

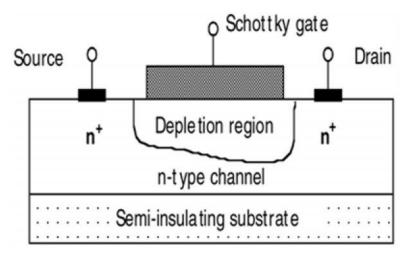

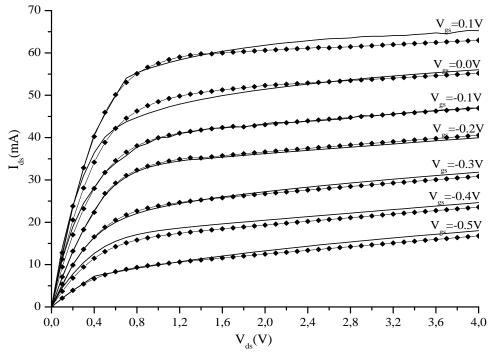

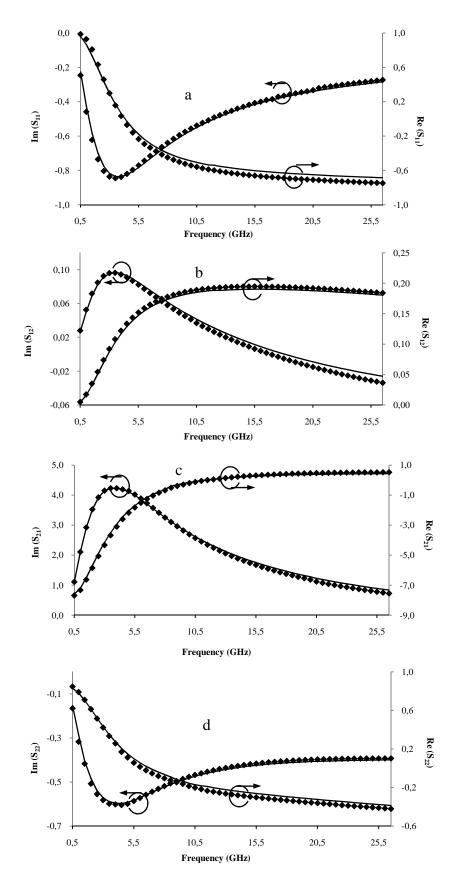

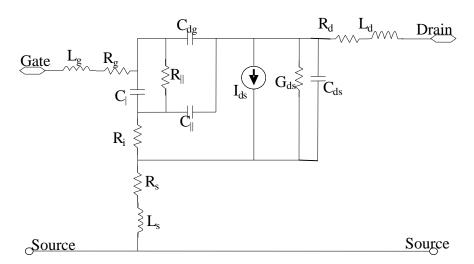

| Figure I.4: Depletion region in MESFET with positive drain bias [Yasuto; 2012] 13        |    |